1

# **CENTRAL PROCESSOR**

LOGIC DESCRIPTION

Remington Rand Univac®

DIVISION OF SPERRY RAND CORPORATION

3 1 5 PARK AVENUE SOUTH

NEW YORK 10 N Y

#### Section 2

Introduction to the UNIVAC III Logic Components & Assemblies; and a Description of the Cycling Unit

Under Preparation

(Sections 1, 3-8 herewith)

### **CONTENTS**

| Heading        | Litle                                                  |            |  |  |  |  |  |  |

|----------------|--------------------------------------------------------|------------|--|--|--|--|--|--|

|                | SECTION 1. INTRODUCTION AND GENERAL DESCRIPTION        |            |  |  |  |  |  |  |

|                |                                                        |            |  |  |  |  |  |  |

| 1-1.           | Central-Processor Specifications                       | 1-1        |  |  |  |  |  |  |

| 1-2.           | UNIVAC III Central-Processor Logic Features            | 1-2        |  |  |  |  |  |  |

| 1 <b>-</b> 3.  | Four-bit Parallel Transfer                             | 1-2        |  |  |  |  |  |  |

| <b>1-4.</b>    | Overlapping Operation                                  | 1-2        |  |  |  |  |  |  |

| 1 <b>-</b> 5.  | Multiprecision Instructions                            | 1-2        |  |  |  |  |  |  |

| 1-6.           | Priority                                               | 1-2        |  |  |  |  |  |  |

| 1-7.           | Multiply Instructions                                  | 1-2<br>1-2 |  |  |  |  |  |  |

| 1-8.           | Initiate Input-Output Instruction                      | 1-2        |  |  |  |  |  |  |

| 1-9.           | Automatic-Programming Aids                             | 1-3        |  |  |  |  |  |  |

| 1-10.          | Scatter-Read/Gather-Write Control Word                 | 1-3        |  |  |  |  |  |  |

| 1-11.          | Number-System Compatibility                            | 1-3        |  |  |  |  |  |  |

| 1-12.          | Checking Features                                      | 1-3        |  |  |  |  |  |  |

| 1-13.          | Functional Components of Central Processor             | 1-3        |  |  |  |  |  |  |

| 1-14.          | Instruction-Control Section                            | 1-3        |  |  |  |  |  |  |

| 1-15.<br>1-16. | Storage-Address Section                                | 1-3        |  |  |  |  |  |  |

| 1-16.<br>1-17. | Field-Select Section                                   | 1-3        |  |  |  |  |  |  |

| 1-17.          | Memory-Address Section                                 | 1-4        |  |  |  |  |  |  |

| 1-19.          | Arithmetic Section                                     | 1-4        |  |  |  |  |  |  |

| 1-20.          | Input-Output Control Section                           | 1-4        |  |  |  |  |  |  |

| 1-21.          | Priority Section                                       | 1-4        |  |  |  |  |  |  |

| 1-22.          | Write Register                                         | 1-4        |  |  |  |  |  |  |

| 1-23.          | Sense-Flip-Flop Section                                | 1-4        |  |  |  |  |  |  |

| 1-24.          | Interrupt Section                                      | 1-4        |  |  |  |  |  |  |

| 1-25.          | Typewriter and Real-Time-Clock Section                 | 1-6        |  |  |  |  |  |  |

| 1-26.          | Cycling-Unit Section and Display Section               | 1-6        |  |  |  |  |  |  |

| 1-27.          | UNIVAC III Word Formats                                | 1-6        |  |  |  |  |  |  |

| 1-28.          | Data Words ,                                           | 1-6        |  |  |  |  |  |  |

| 1-29.          | Instruction Word                                       | 1-6        |  |  |  |  |  |  |

| 1-30.          | Input-Output Specification Words                       | 1-7        |  |  |  |  |  |  |

| 1-31.          | Control Words                                          | 1-7        |  |  |  |  |  |  |

| 1-32.          | Data Flow in the UNIVAC III Central Processor          | 1-8        |  |  |  |  |  |  |

| 1-33.          | Data Flow During an Instruction Call                   | 1-8        |  |  |  |  |  |  |

| 1-34.          | Data Flow when Reading the Instruction from            | 1 0        |  |  |  |  |  |  |

|                | Memory                                                 | 1-8        |  |  |  |  |  |  |

| 1-35.          | Data Flow During the First Operand Call                | 1-8        |  |  |  |  |  |  |

| 1-36.          | Data Flow During the Field Selection and               | 1-8        |  |  |  |  |  |  |

| 4 05           | Indirect Addressing                                    | 1-10       |  |  |  |  |  |  |

| 1-37.          | Data Flow During Multiprecision Instructions           | 1-10       |  |  |  |  |  |  |

| 1-38.          | Data Flow During Instructions which use the Main Adder | 1-10       |  |  |  |  |  |  |

| 1_90           | Adder                                                  | 1-11       |  |  |  |  |  |  |

| 1-39.          | High, Low, and Equal Flip-Flops                        | 1-12       |  |  |  |  |  |  |

| 1-40.          | Extract Instructions                                   | 1-12       |  |  |  |  |  |  |

| 1-41.<br>1-42. | Multiply and Divide Instructions                       | 1-12       |  |  |  |  |  |  |

| 1-42.<br>1-43. | Store- and Load-Accumulator Instructions               | 1-12       |  |  |  |  |  |  |

| 1-43.<br>1-44. | Data Flow During Instructions which Transfer Data      |            |  |  |  |  |  |  |

| 1-44.          | Between the Storage-Address Registers and              |            |  |  |  |  |  |  |

|                | Memory                                                 | 1-13       |  |  |  |  |  |  |

|                |                                                        |            |  |  |  |  |  |  |

| Heading        | Title                                          | Page       |

|----------------|------------------------------------------------|------------|

| 1-45.          | Data Flow During Instructions which Store the  |            |

|                | Contents of a Storage-Address Register         | 1-14       |

| 1-46.          | Data Flow During Instructions which Load a     |            |

|                | Storage-Address Register                       | 1-14       |

| 1-47.          | Data Flow During Instructions which Modify and |            |

|                | Compare the Contents of an Index Register      | 1-14       |

| 1-48.          | Data Flow During Shift Instructions            | 1-15       |

| 1-49.          | Data Flow During Miscellaneous Instructions    | 1-15       |

| 1-50.          | Sense-Flip-Flop Instructions                   | 1-15       |

| 1-51.          | Interrupt Instructions                         | 1-15       |

| 1-52.          | Data Flow During the Expand Instruction        | 1-16       |

| <b>1-53.</b>   | Data Flow During a Compress Instruction        | 1-16       |

| 1-54.          | Data Flow During Transfer Instructions         | 1-17       |

| 1 <b>-</b> 55. | Data Flow During Zero-Suppress Instruction     | 1-17       |

| 1 <b>-</b> 56. | Data Flow During Typewriter Instructions       | 1-17       |

| <b>1-</b> 57.  | Data Flow During Input-Output Operations       | 1-18       |

| 1-58.          | Data Flow when Transferring the Specification  |            |

|                | Word to Memory                                 | 1-19       |

| 1 <b>-</b> 59. | Data Flow when Transferring the Specification  |            |

|                | Word From the Standby Location                 | 1-21       |

| 1-60.          | Data Flow for Data Word for All Devices        |            |

|                | Except Tape Units                              | 1-21       |

| 1-61.          | Data Flow for Transferring the Scatter-Read/   |            |

| 4 40           | Gather-Write Control Word                      | 1-21       |

| 1-62.          | Data Flow for Words During Tape Operations     | 1-21       |

| 1-63.          | UNIVAC III Instructions                        | 1-21       |

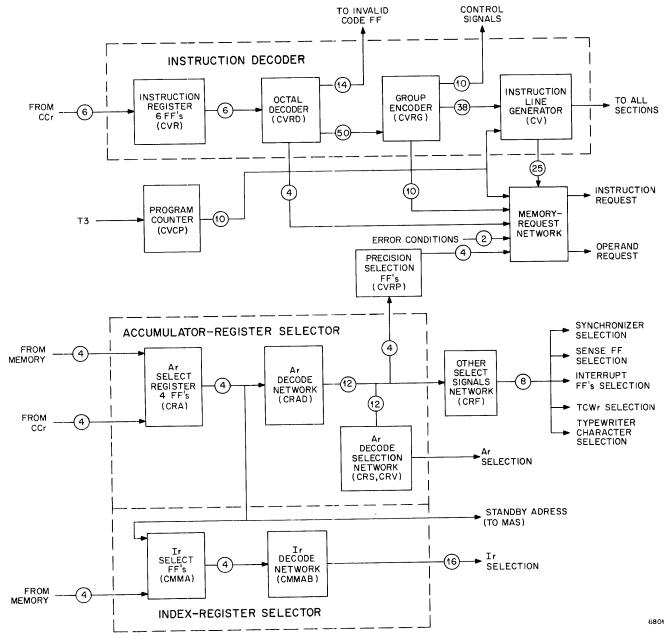

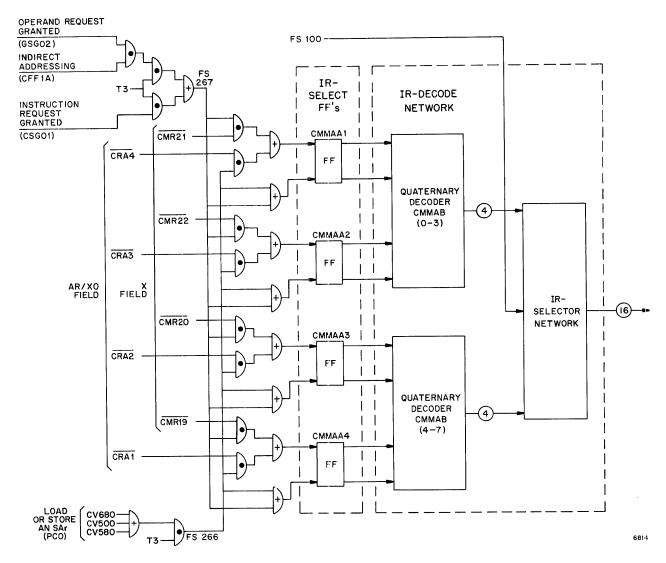

| 3-1.           | Introduction                                   | 3-1        |

| 3-2.           | Instruction Decoder                            | 3-1        |

| 3-3.           | Program Counter                                | 3-1        |

| 3-4.           | Accumulator-Register Selector                  | 3-2        |

| 3 <b>-</b> 5.  | Index-Register Selector                        | 3-2        |

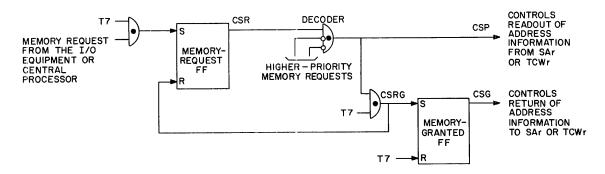

| 3-6.           | Memory-Request Network                         | 3-3        |

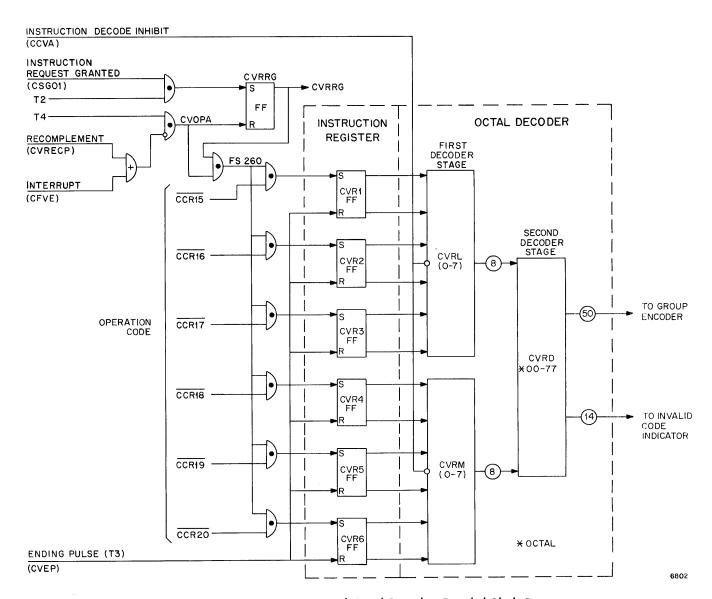

| 3-7.           | Instruction Decoder                            | 3-3        |

| 3-8.           | Instruction Register                           | 3-3        |

| 3-9.           | Octal Decoder                                  | 3-4        |

| 3-10.          | Group Encoder                                  | 3-4        |

| 3-11.<br>3-12. | Instruction-Line Generator                     | 3-4        |

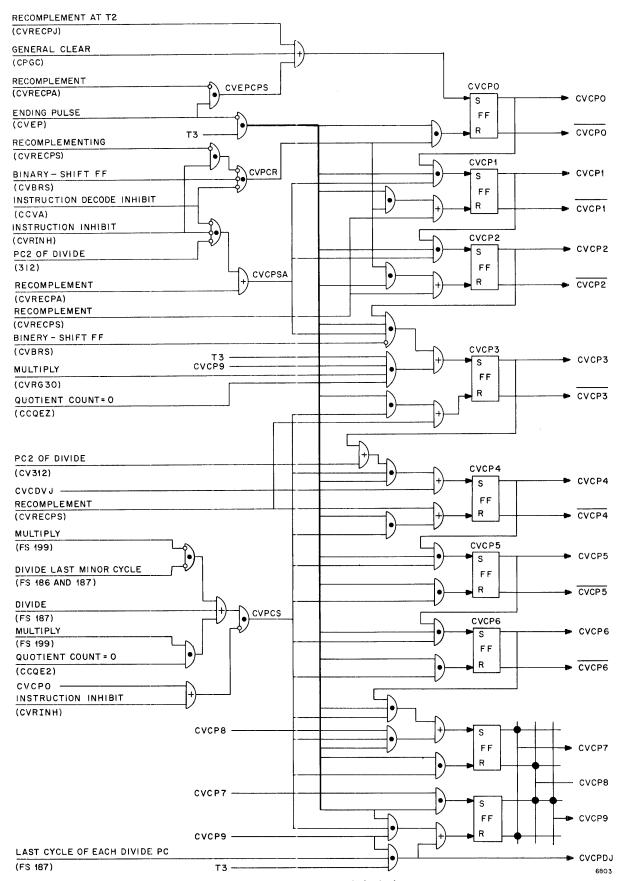

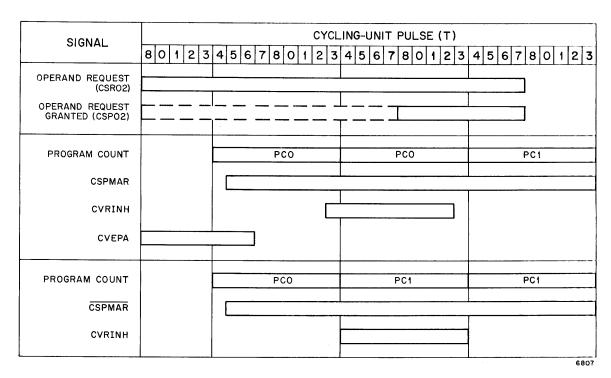

| 3-12.<br>3-13. | Program Counter                                | 3-5<br>3-5 |

| 3-13. 3-14.    | General Operation                              | 3-5<br>3-5 |

| 3-15.          | Normal Cycle                                   | 3-5        |

| 3-16.          | Shift Cycle                                    | 3-5        |

| 3-17.          | Recomplement Cycle                             | 3-5        |

| 3-18.          | Multiply Cycle                                 | 3-8        |

| 3-19.          | Divide Cycle                                   | 3-8        |

| 3-20.          | Accumulator-Register Selector                  | 3-8        |

| 3-21.          | AR-Select Flip-Flops                           | 3-8        |

| 3-22.          | AR-Decode Network                              | 3-8        |

| 3-23.          | AR-Selection Network                           | 3-9        |

| 3-24.          | Function Signals 235, 236, 237, and 238        | 3-10       |

| 3-25.          | Function Signal 128                            | 3-10       |

| 3-26.          | Function Signal 129                            | 3-10       |

| 3-27.          | Selection of Accumulator Registers             | 3-11       |

| 3-28.          | Precision Selection                            | 3-12       |

| 3-29.          | Other Selection Functions of the AR-Select     |            |

|                | Flip-Flops                                     | 3-13       |

| 3-30.          | Index-Register Selector                        | 3-13       |

| Heading                                                                                 | Title                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                           |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

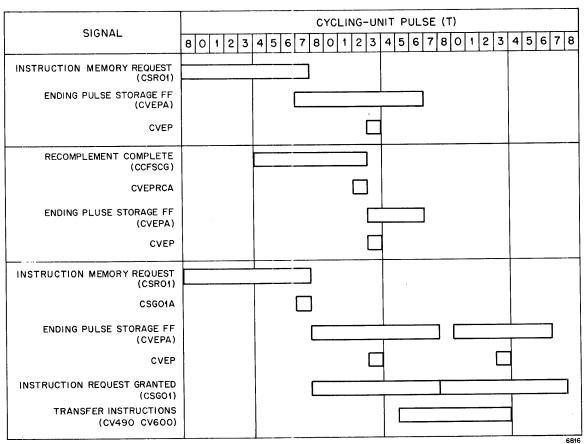

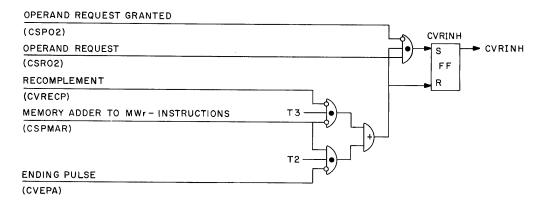

| 3-31. 3-32. 3-33. 3-34. 3-35. 3-36. 3-37. 3-38. 3-39. 3-40. 3-41. 3-42.                 | Instruction Memory Requests Instruction-Control Signal Multiprecision Instructions Zero-Suppress Instruction Shift Instructions Error Conditions Operand Memory Requests Instruction-Control Signals The CVEP Signal The CVRINH Signal The CVRECP Signal The CVRECP Signal The CCVA Signal                                                                                             | 3-13<br>3-13<br>3-14<br>3-15<br>3-15<br>3-15<br>3-15<br>3-16<br>3-19<br>3-19                   |

|                                                                                         | SECTION 4. PRIORITY SECTION                                                                                                                                                                                                                                                                                                                                                            |                                                                                                |

| 4-1.<br>4-2.<br>4-3.<br>4-4.<br>4-5.<br>4-6.<br>4-7.<br>4-8.<br>4-9.                    | Introduction                                                                                                                                                                                                                                                                                                                                                                           | 4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-4<br>4-4<br>4-5                                           |

|                                                                                         | SECTION 5. COMPUTER-CONTROL REGISTER                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

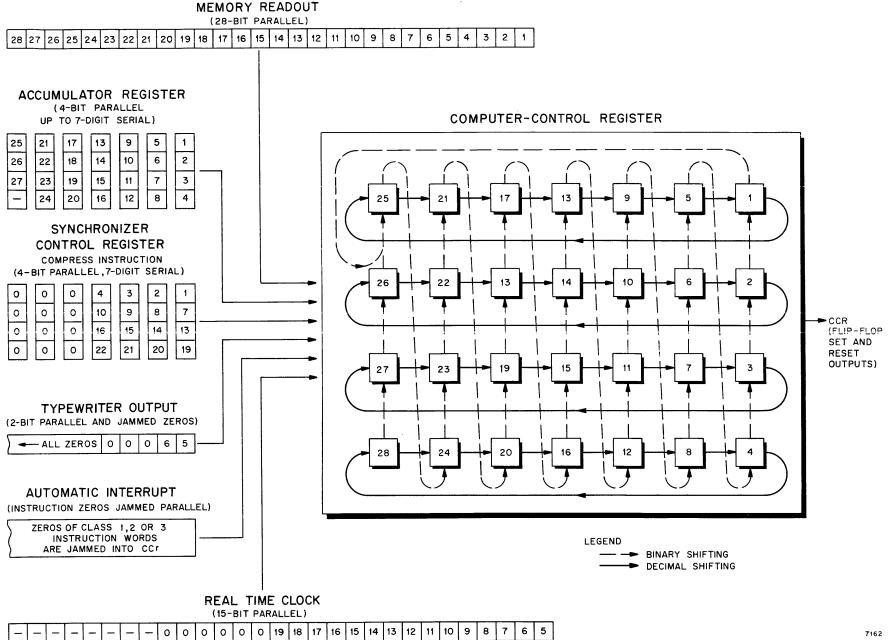

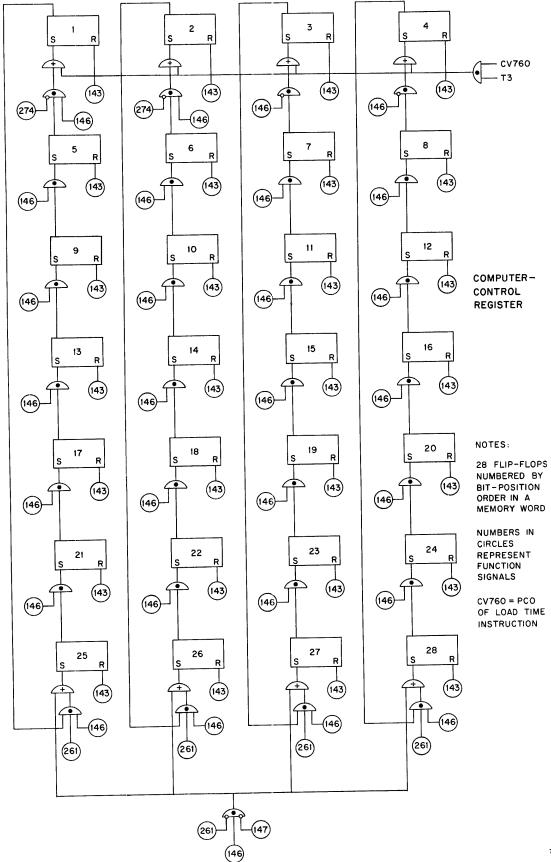

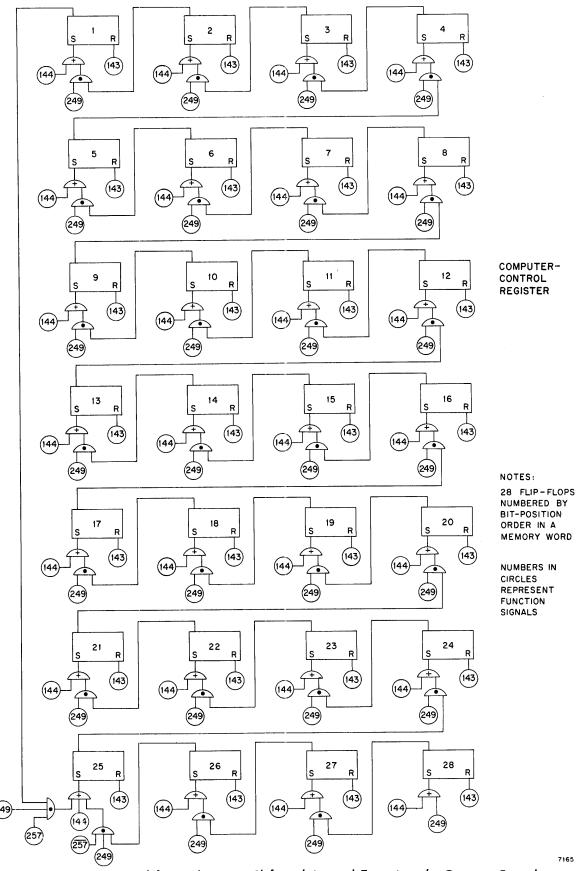

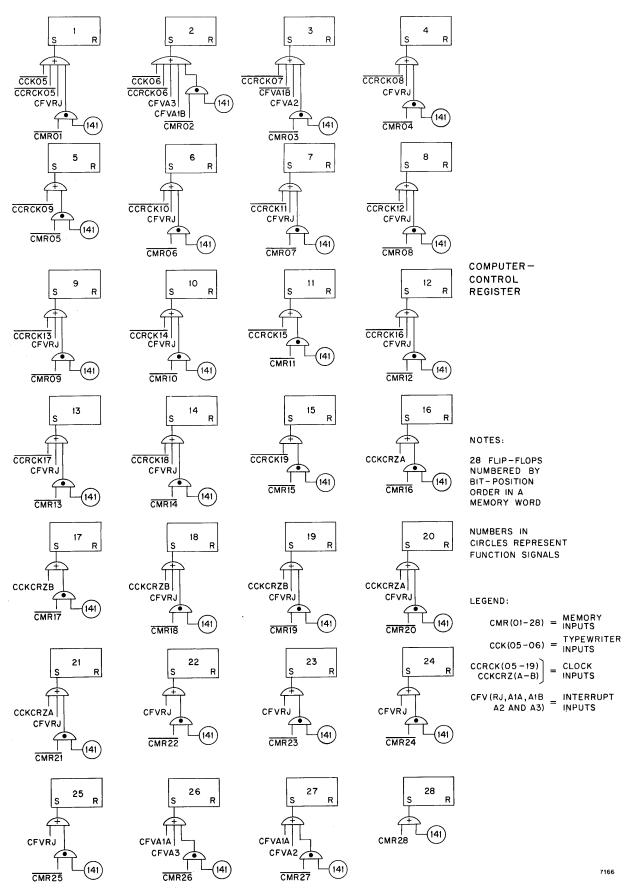

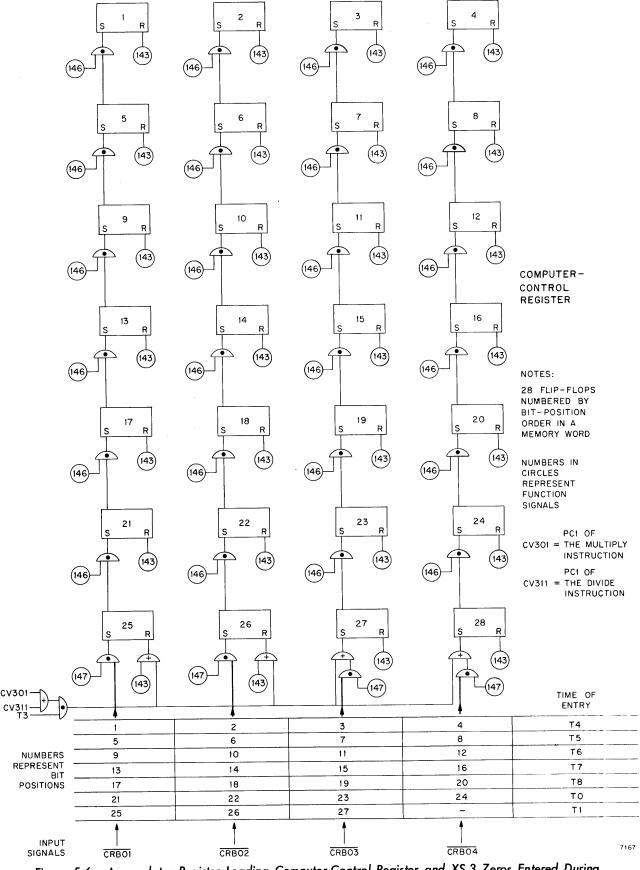

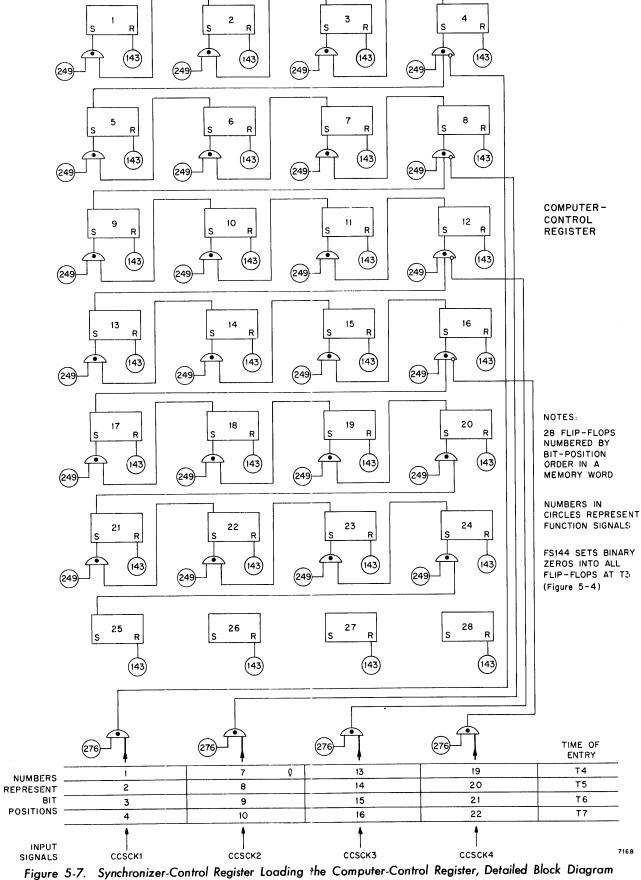

| 5-1. 5-2. 5-3. 5-4. 5-5. 5-6. 5-7.  5-8. 5-9. 5-10. 5-11. 5-12. 5-13. 5-14. 5-15. 5-16. | Introduction General Operation Logic of Computer-Control Register Register Functions Resetting Jamming Binary Zeros Decimal Shifting and Circular-Decimal Shifting Binary Shifting and Circular-Binary Shifting Register Inputs Memory Input Typewriter Input Real-Time-Clock Input Interrupt Inputs Accumulator-Register Inputs Synchronizer-Control-Register Inputs Register Outputs | 5-1<br>5-1<br>5-1<br>5-3<br>5-3<br>5-3<br>5-5<br>5-5<br>5-5<br>5-5<br>5-8<br>5-8<br>5-8<br>5-8 |

|                                                                                         | SECTION 6. STORAGE-ADDRESS SECTION                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

| 6-1.<br>6-2.<br>6-3.<br>6-4.<br>6-5.<br>6-6.                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                           | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-4<br>6-4                                                  |

| Heading        | Title                                                | Page         |

|----------------|------------------------------------------------------|--------------|

| 6-8.           | Selection of Memory-Address Counters                 | 6-4          |

| 6-9.           | Selection of TCWr's                                  | 6-6          |

| 6-10.          | SAr and TCWr Outputs                                 | 6-8          |

|                | SECTION 7. MEMORY-ADDRESS SECTION                    |              |

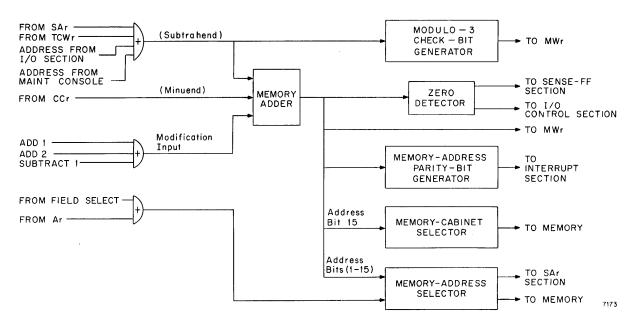

| 7-1.<br>7-2.   | Introduction                                         | 7-1<br>7-2   |

| 7-2.<br>7-3.   | Memory Adder                                         | 7-2          |

| 7-4.           | Minuend Inputs                                       | 7-3          |

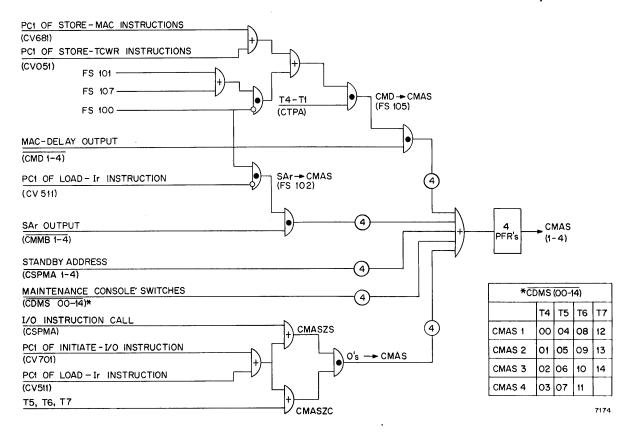

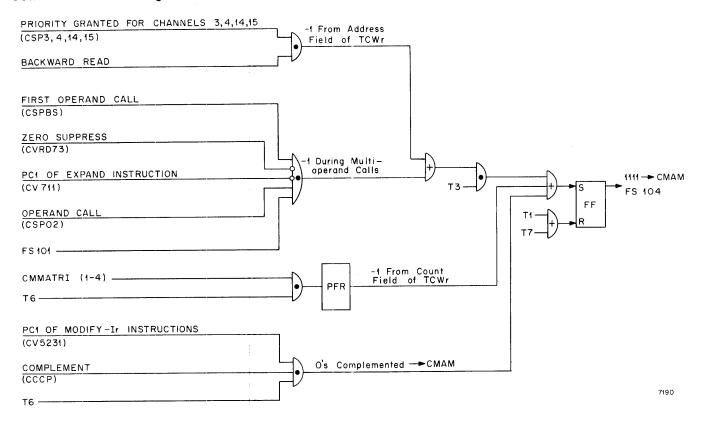

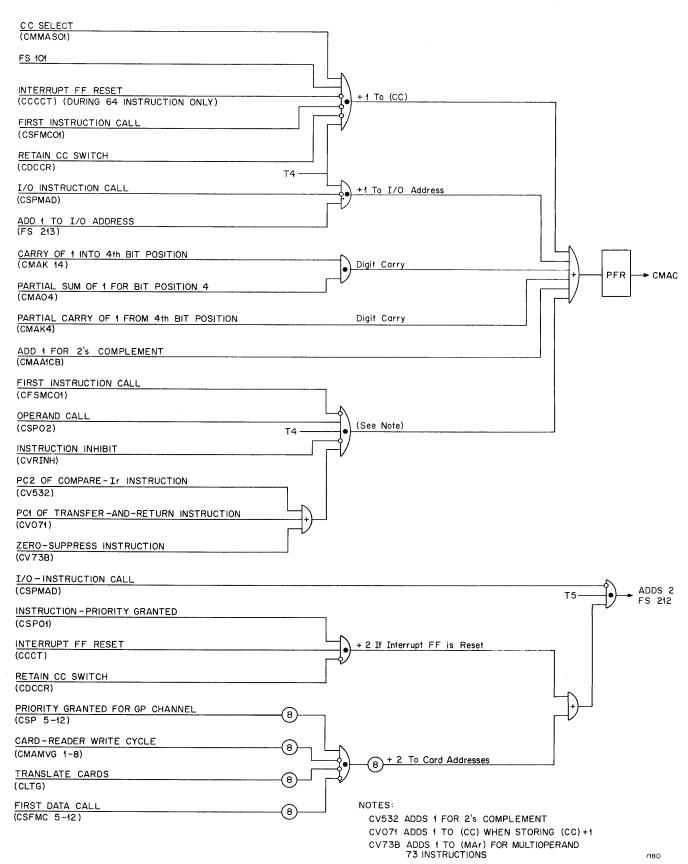

| 7-5.           | CMAC Pulseformer Inputs                              | 7-5          |

| 7-6.           | Memory-Adder Addition Logic                          | 7-6          |

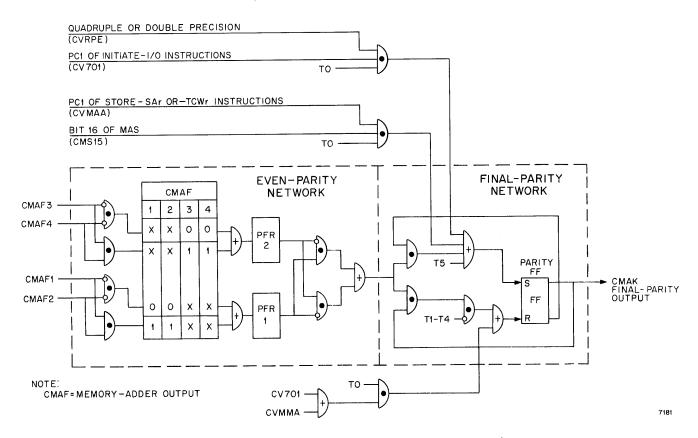

| 7-7.           | Memory-Address Parity Generator                      | 7-8          |

| 7-8.           | Generation of Parity Bit From the Memory-Adder       |              |

| 7-9.           | Output                                               | 7-8          |

| 7-10.          | TCWr Instructions                                    | 7-10         |

| 7 11           | Instruction                                          | 7-10<br>7-10 |

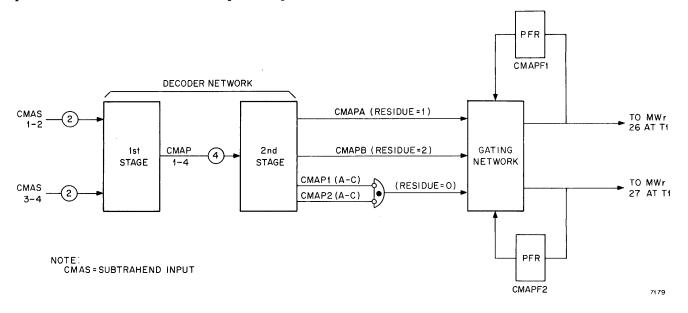

| 7-11.<br>7-12. | Modulo-3 Check-Bit Generation                        | 7-10         |

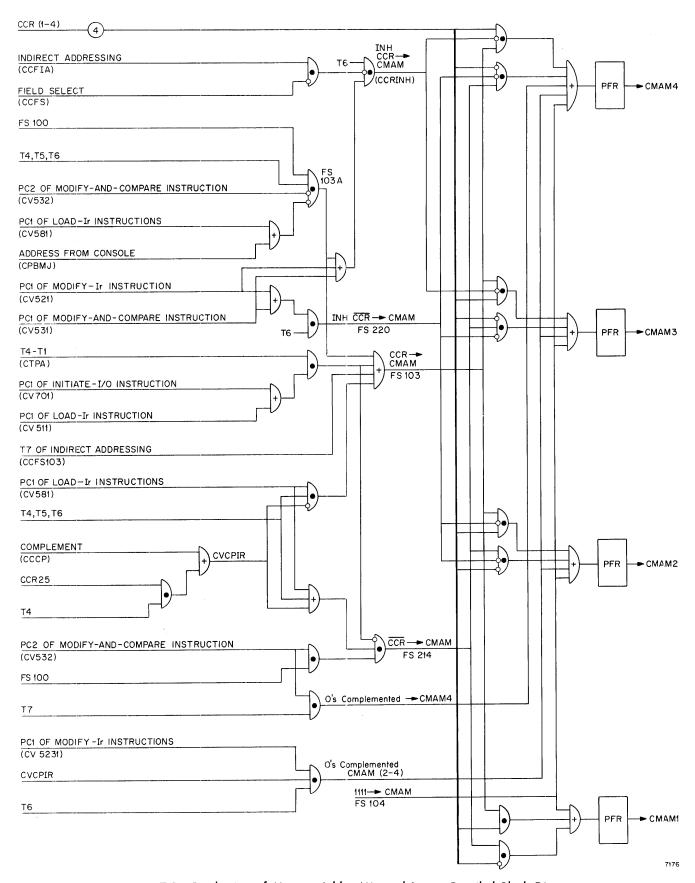

| 7-12.<br>7-13. | Memory-Address Selector                              | 7-12         |

| 7-14.          | Memory-Address Selector Inputs                       | 7-12         |

| 7-15.          | Memory-Cabinet Selector                              | 7-15         |

| 7-16.          | Zero-Detector Flip-Flop                              | 7-16         |

| 7-17.          | Tape Operation                                       | 7-16         |

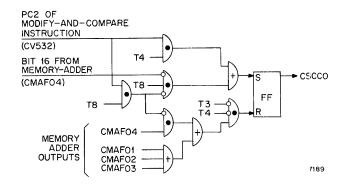

| 7-18.          | The 53 Instruction                                   | 7-16         |

|                | SECTION 8. MEMORY-WRITE REGISTER                     |              |

| 8-1.           | Introduction                                         | 8-1          |

| 8-2.           | Central-Processor Format                             | 8-1          |

| 8-3.           | Accumulator Register                                 | 8-1          |

| 8-4.           | Memory Adder                                         | 8-2          |

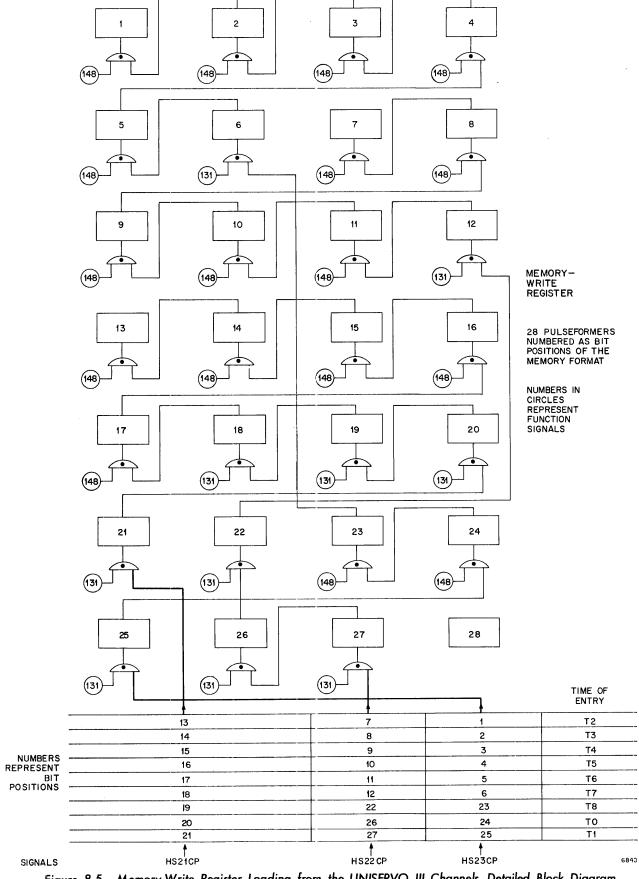

| 8-5.           | UNISERVO III Format                                  | 8-2          |

| 8-6.           | Input-Output Format                                  | 8-4          |

| 8-7.           | Computer-Control-Register Format, Expand Instruction |              |

| 8-8.           | Only                                                 | 8-7<br>8-9   |

| 8-9.           | Summary of Functions                                 | 8-9          |

|                |                                                      |              |

| APPEN          | NDIX A. ENGINEERING-DRAWING SOURCES OF ILLUSTRATION  | ONS          |

|                | ILLUSTRATIONS                                        |              |

|                |                                                      |              |

| Figure         | Title                                                | Page         |

| 1-1.           | Central Processor, Functional Block Diagram          | 1-5          |

| 1-2.           | Data Flow During an Instruction Call,                |              |

| -              | Functional Block Diagram                             | 1-9          |

|                | ·                                                                                                 |              |

|----------------|---------------------------------------------------------------------------------------------------|--------------|

| 1-3.           | Data Flow During Multiprecision Instructions, Functional Block Diagram                            | 1-10         |

| 1-4.           | Data Flow During Instructions Which Use the Main Adder, Functional Block Diagram                  | 1-11         |

| 1-5.           | Example of Double-Precision Add with Carries, Functional                                          |              |

| 1-6.           | Block Diagram                                                                                     | 1-12         |

| 1-7.           | Locations, Diagram                                                                                | 1-12         |

| 1-8.           | Locations, Diagram                                                                                | 1-13         |

| -              | Store Instructions, Functional Block Diagram                                                      | 1-13         |

| 1-9.           | Data Flow During Index-Register Modify and Compare Instructions, Functional Block Diagram         | 1-14         |

| 1-10.          | Shifting Right with Right Shifts or with Left Shifts, Diagram                                     | 1-15         |

| 1-11.          | Data Flow During Double-Precision Two-Digit Right Shift, Diagram                                  | 1-16         |

| 1-12.          | Data Flow During Double-Precision Two-Digit Left Shift, Diagram                                   | 1-17         |

| 1 <b>-1</b> 3. | Data Flow During Typewriter Interrupt, and Sense-Flip-Flop Instructions, Functional Block Diagram | 1-18         |

| 1-14.          | Data Flow During Expand and Compress Instructions, Functional Block Diagram                       | 1-19         |

| 1-15.          | Data Flow During Input-Output Operations, Functional                                              | 1 10         |

|                | Block Diagram                                                                                     | 1-20         |

| 3-1.           | Instruction-Control Section, Functional Block Diagram                                             | 3-2          |

| 3-2.           | Instruction Register and Octal Decoder,  Detailed Block Diagram                                   | 3-3          |

| 3-3.           | Program Counter, Detailed Block Diagram                                                           | 3-6          |

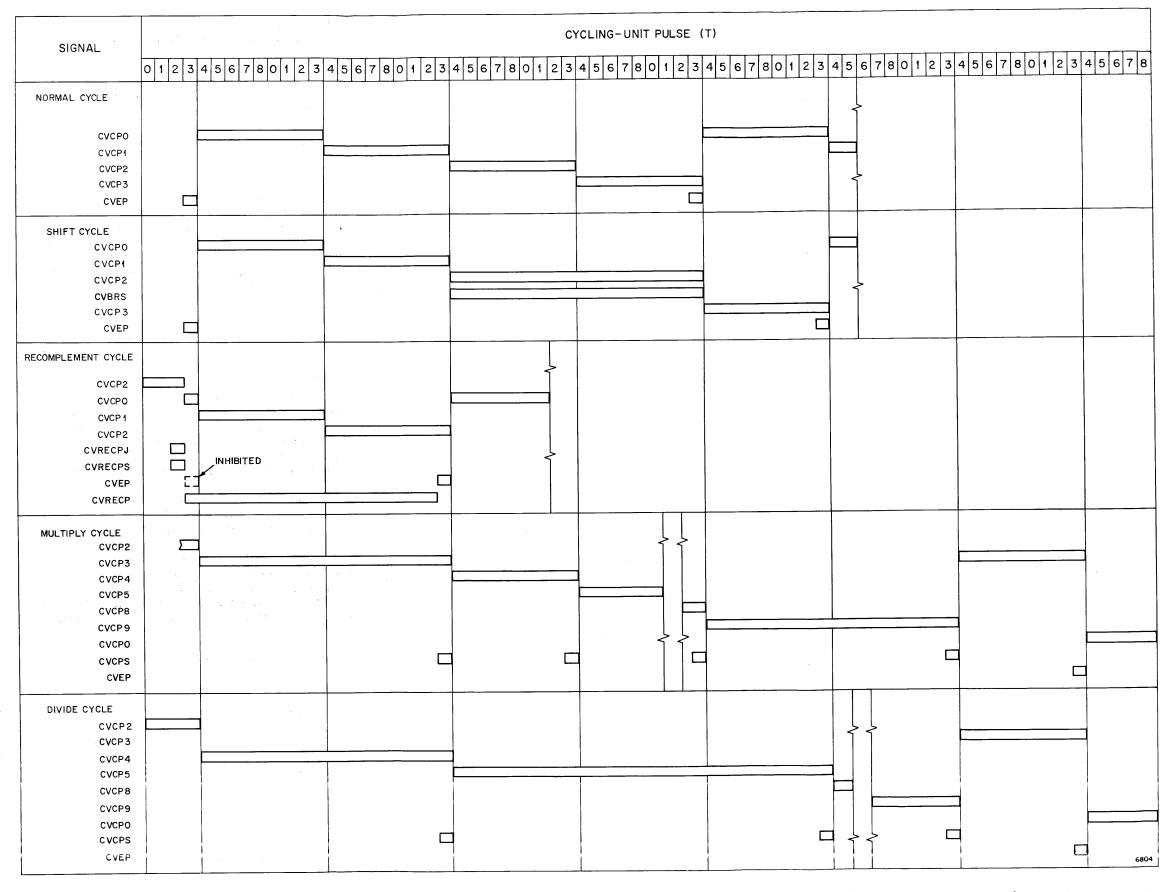

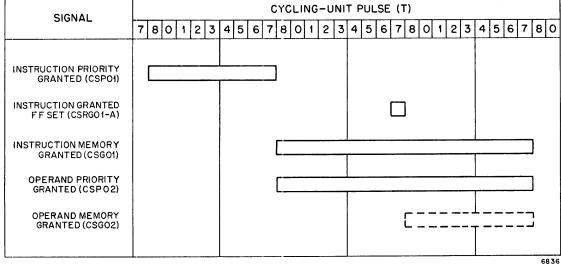

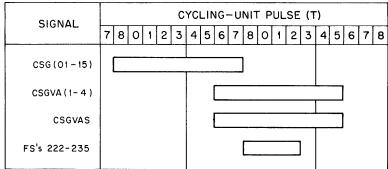

| 3-4.           | Timing Diagram for Typical Program Cycles                                                         | 3-7          |

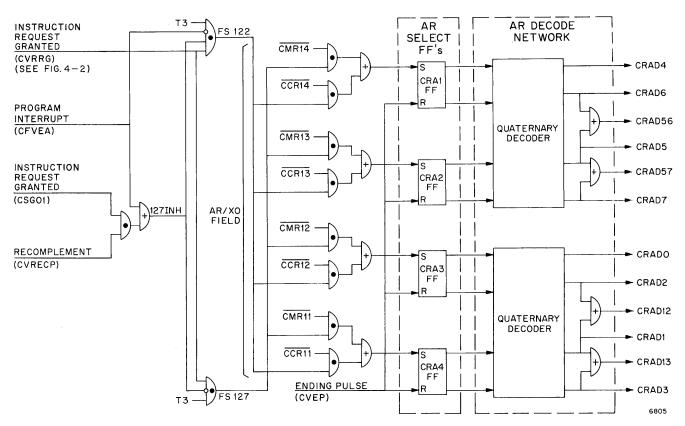

| 3-5.           | AR-Select FF's and Decode Network, Detailed Block Diagram                                         | 3-9          |

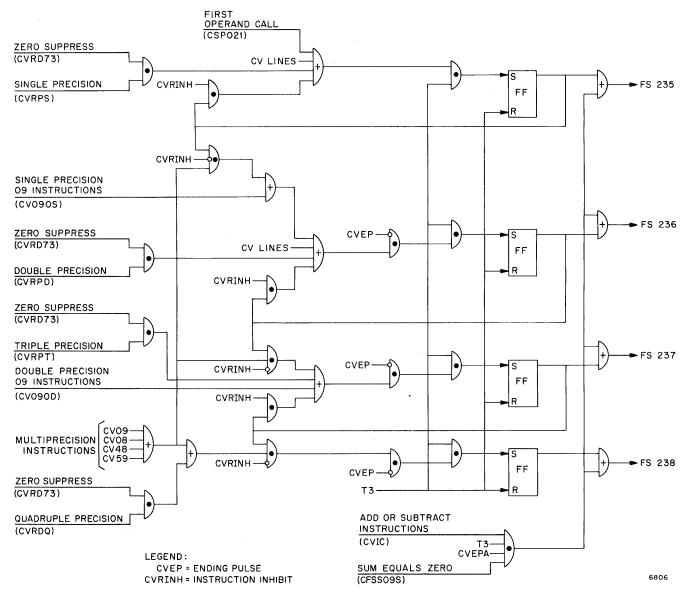

| 3-6.           | Production of Function Signals 235, 236, 237, and 238, Detailed Block Diagram                     | 3-11         |

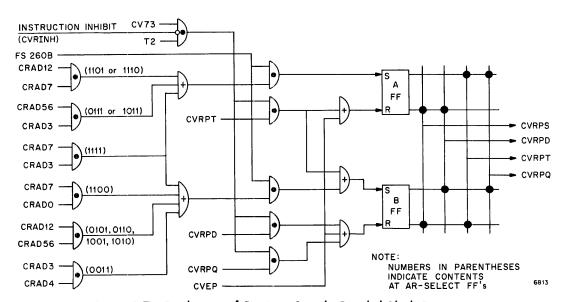

| 3-7.           | Production of Precision Signals, Detailed                                                         | 3-12         |

| • •            | Block Diagram Detailed Block Diagram                                                              | 3-14         |

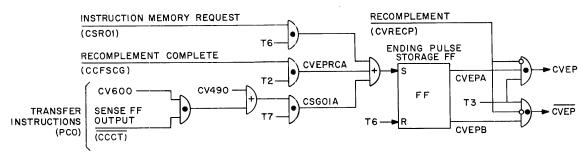

| 3-8.<br>3-9.   | Index-Register Selector, Detailed Block Diagram Production of the CVEP Signal, Detailed           | 9-14         |

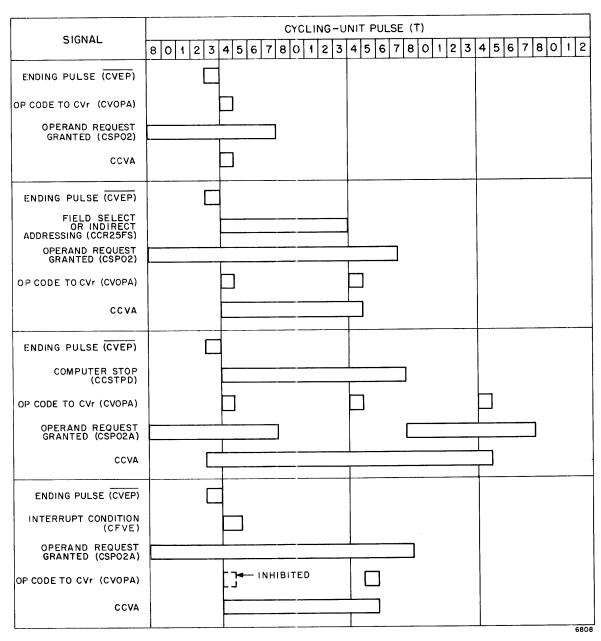

| _              | Block Diagram and Timing Diagram                                                                  | 3-16         |

| 3-10.          | Production of the CVRINH Signal, Detailed Block Diagram and Timing Diagram                        | 3-17         |

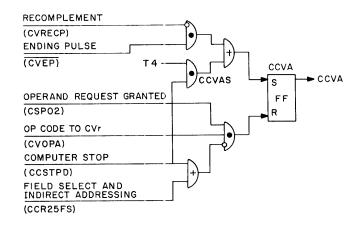

| 3-11.          | Production of the CCVA Signal, Detailed                                                           | 3-18         |

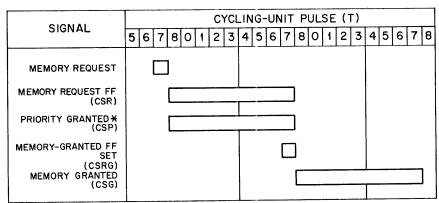

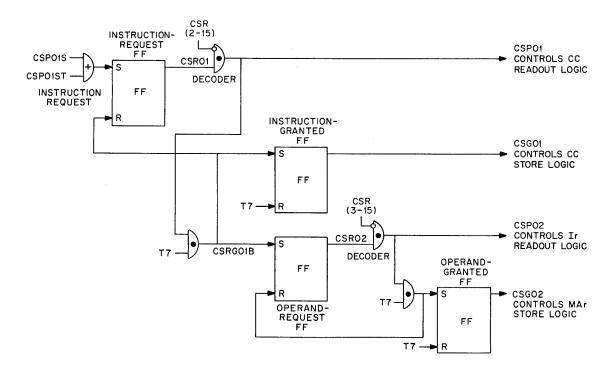

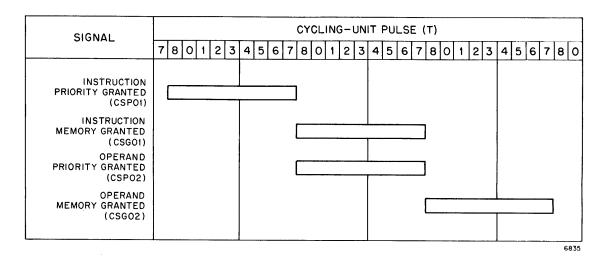

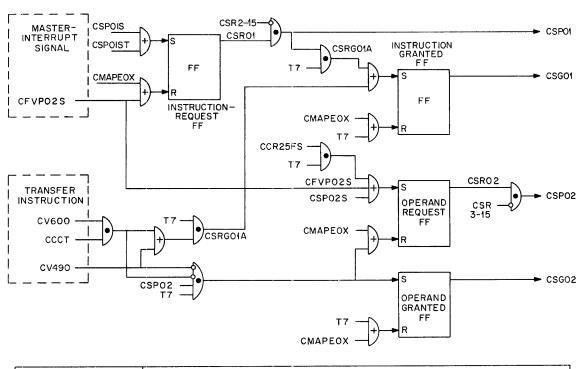

| 4-1.           | Block Diagram and Timing Diagram Typical Priority Channel, Detailed Block                         | 4-2          |

| 4-2.           | Diagram                                                                                           |              |

| 4-3.           | Diagram                                                                                           | 4-3          |

| 5-1.           | Diagram                                                                                           | 4-4          |

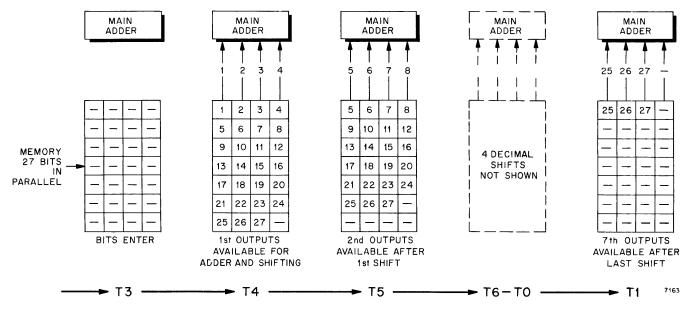

|                | Diagram                                                                                           | 5-2          |

| 5-2.           | Example of the Transfer of a Word from Memory Through the Computer-Control Register to            | _            |

| 5-3.           | Main Adder, Functional Block Diagram Decimal Shift, Circular-Decimal Shift, Binary-               | 5 <b>-</b> 3 |

| υ-υ,           | Zero Entries into the Computer-Control                                                            |              |

|                | Register, Detailed Block Diagram                                                                  | 5-4          |

| 5-4.           | Binary Shift, Circular-Binary Shift, and Jammed                                                   |              |

|                | Zeros into the Computer-Control Register, Detailed Block Diagram                                  | 5-6          |

| Figure | Title                                                                                                                           | Page         |

|--------|---------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5-5.   | Parallel Inputs from Memory, Real-Time Clock, and Typewriter into the Computer-Control                                          |              |

| 5-6.   | Register, Detailed Block Diagram                                                                                                | 5-7          |

| 5-7.   | Multiply and Divide, Detailed Block Diagram Synchronizer-Control Register Loading the Computer-Control Register, Detailed Block | 5-9          |

| 6-1.   | Diagram                                                                                                                         | 5-10         |

| 6-2.   | Diagram                                                                                                                         | 6-1          |

|        | Word-Register Selection, Detailed Block Diagram                                                                                 | 6-3          |

| 6-3.   | Production of Storage-Address-Register and Tape-Control-Word-Register Function Signals,                                         | 0.5          |

| 6-4.   | Detailed Block Diagram                                                                                                          | 6-5<br>6-7   |

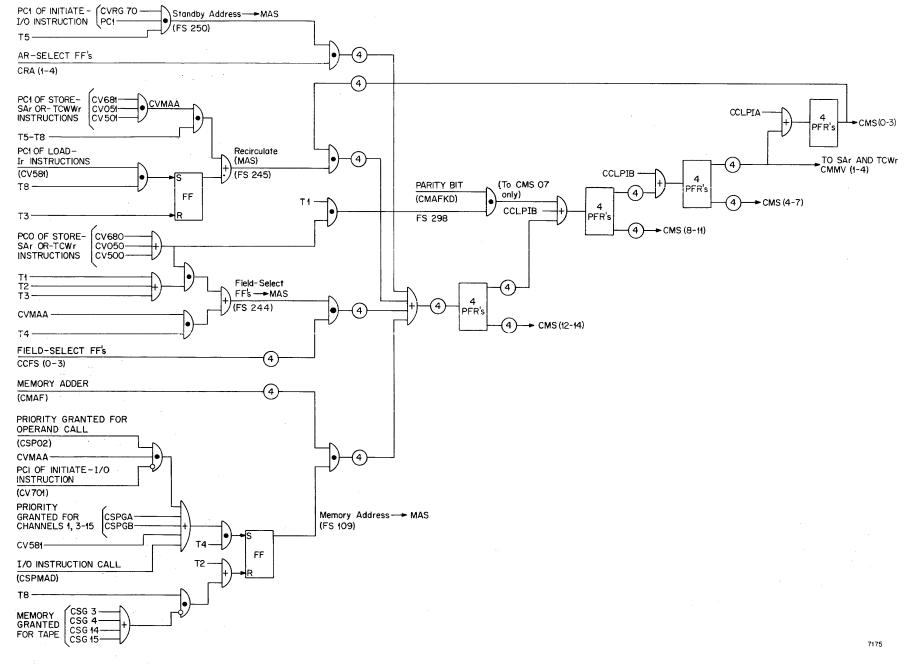

| 7-1.   | Memory-Address Section, Functional Block                                                                                        |              |

| 7-2.   | Diagram                                                                                                                         | 7 <b>-</b> 1 |

| 7-3.   | Production of Memory-Adder Minuend Inputs, De-                                                                                  | 7-4          |

| 7-4.   | tailed Block Diagram                                                                                                            | 7 <b>-</b> 4 |

| 7-5.   | Production of Add-1 (CMAC) and Add-2 (Function Signal 212) Signals, Detailed Block Diagram                                      | 7-7          |

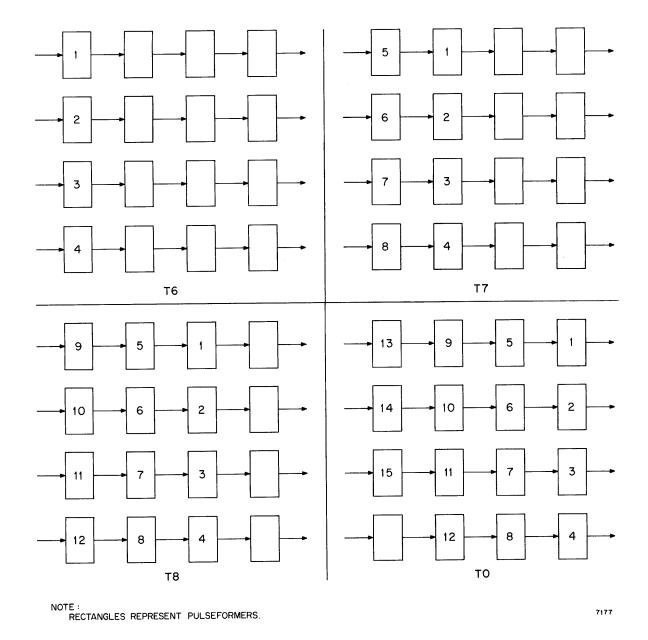

| 7-6.   | Memory-Adder Parity-Bit Generation, Detailed Block Diagram                                                                      | 7-9          |

| 7-7.   | Modulo-3 Check-Bit Generation, Detailed Block Diagram                                                                           | 7-11         |

| 7-8.   | Memory-Address Selector, Functional Block Diagram                                                                               | 7-13         |

| 7-9.   | Memory-Address Selector, Detailed Block Diagram                                                                                 | 7-14         |

| 7-10.  | Cabinet Selector, Detailed Block Diagram                                                                                        | 7-15         |

| 7-11.  | Zero Detector, Detailed Block Diagram                                                                                           | 7-16         |

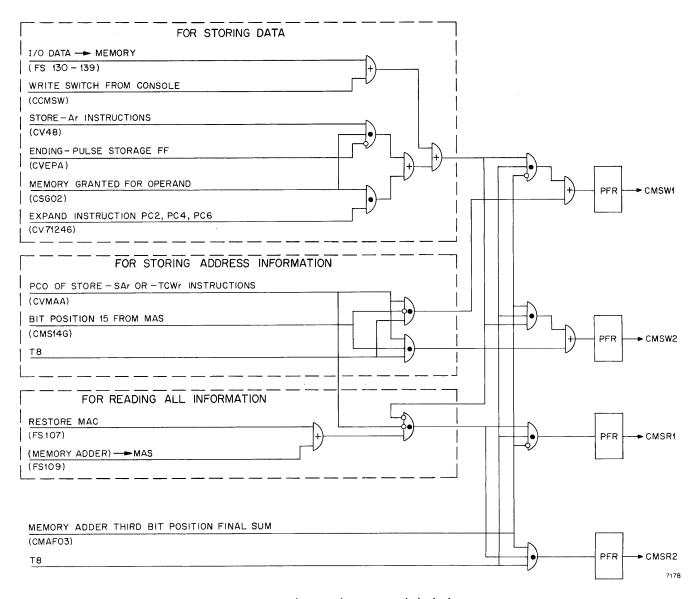

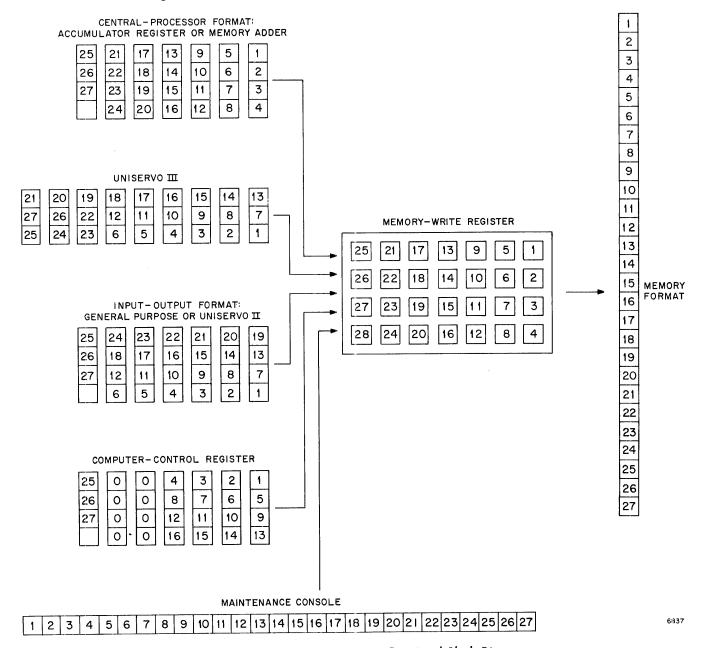

| 8-1.   | Memory-Write Register, Functional Block Diagram                                                                                 | 8-2          |

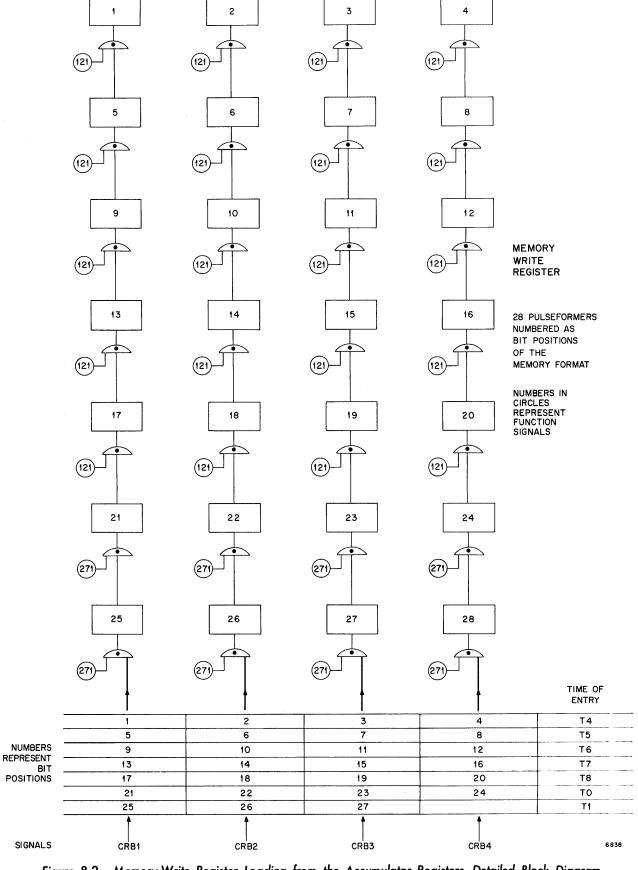

| 8-2.   | Memory-Write Register Loading from the Accumulator Registers, Detailed Block Diagram                                            | 8-3          |

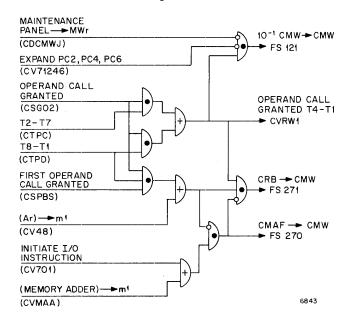

| 8-3.   | Production of CVRW1 and Function Signals 121, 270, and 271, Detailed Block Diagram                                              | 8-4          |

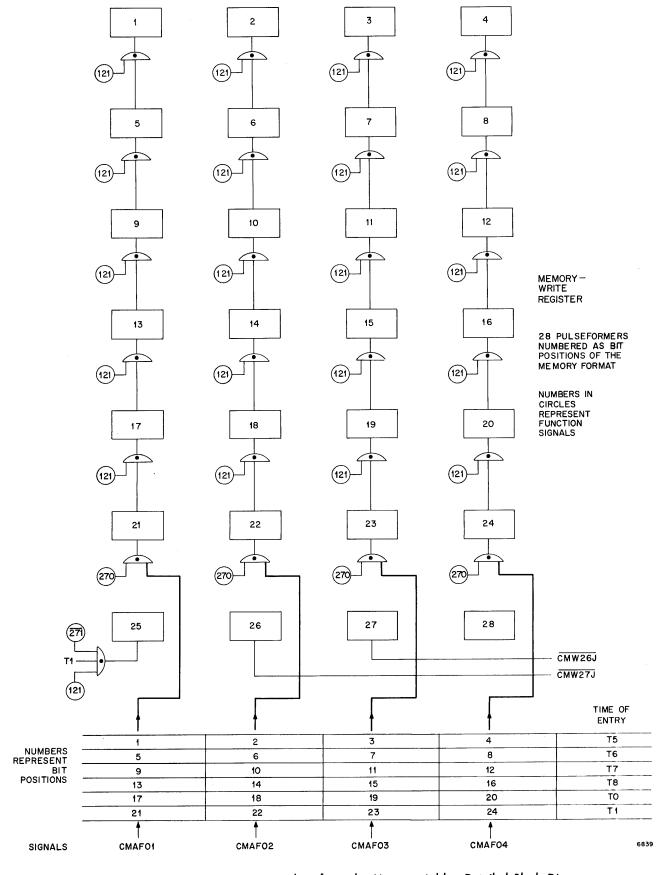

| 8-4.   | Memory-Write Register Loading from the Memory Adder, Detailed Block Diagram                                                     | 8-5          |

| 8-5.   | Memory-Write Register Loading from the UNISERVO III Channels, Detailed Block Dia- gram                                          | 8-6          |

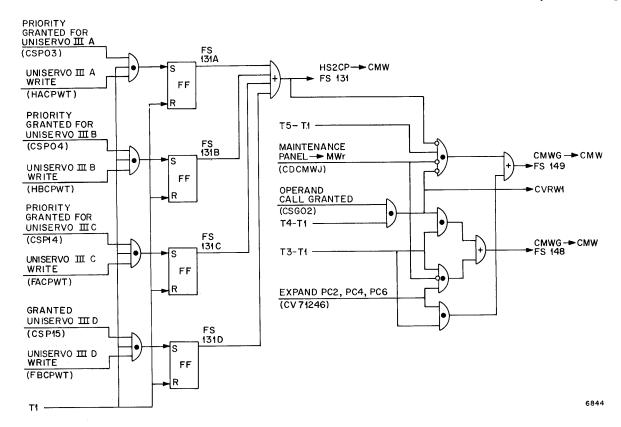

| 8-6.   | Production of Function Signals 131, 148, and 149, Detailed Block Diagram                                                        | 8-7          |

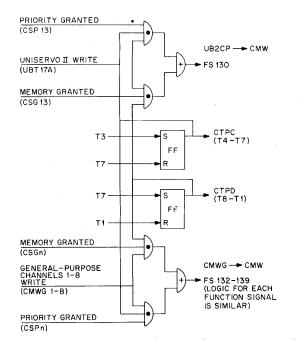

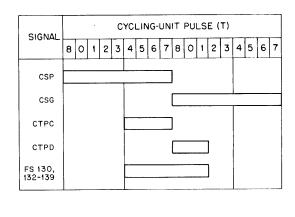

| 8-7.   | Memory-Write Register Loading from UNISERVO II and General-Purpose Channels, Detailed Block                                     | 0.0          |

| 8-8.   | Diagram Production of Function Signals 130, 132 through 139, Detailed Block Diagram                                             | 8 <b>-</b> 8 |

| 8-9.   | Memory-Write Register Loading from the Computer-Control Register During Expand In-                                              | o <b>-</b> 8 |

| 8-10.  | struction, Detailed Block Diagram                                                                                               | 8-11         |

|        | Detailed Block Diagram                                                                                                          | 8-12         |

### **TABLES**

| Table         | Title                                                                                              | Page        |

|---------------|----------------------------------------------------------------------------------------------------|-------------|

| 1-1.          | UNIVAC III Instructions                                                                            | 1-21        |

| 1-2.          | Sense-Flip-Flop Instruction Designations                                                           | 1-24        |

| <b>3-1.</b>   | Decoding of AR-Select Flip-Flop Outputs                                                            | 3-10        |

| 3-2.          | Selection of Accumulator Registers During 08-Type Instructions by Function Signals 235 through 238 | 3-12        |

| 3-3.          | Selection of Accumulator Registers During<br>09-Type Instructions by Function Signals              |             |

| 3-4.          | 235 through 238                                                                                    | 3-12        |

| 1 1           | in the AR-Select Flip-Flops                                                                        | 3-13<br>4-1 |

| 4-1.          | Order of Priority Channel                                                                          |             |

| 5 <b>-1</b> . | Interrupt Instruction Words                                                                        | 5-8<br>5-11 |

| 5-2.<br>5-3.  | Computer-Control-Register Outputs                                                                  |             |

|               | Inputs                                                                                             | 5-11        |

| 5-4.          | Summary of Input Sources and Word Formation                                                        | 5-12        |

| 6-1.          | Input and Output Timing of Memory-Address Counter, Index Register, Tape-Control-Word Register      | 6-2         |

| 6-2.          | Production of Function Signal 222 by CSG03                                                         | 6-6         |

| 6-3.          | Tape-Control-Word-Register Input Information                                                       | 6-8         |

| 7 <b>-1.</b>  | Production of the Final Sum and Partial Carry                                                      | 0.0         |

|               | for the First Bit Position                                                                         | 7-8         |

| 7-2.          | Production of Partial Sums and Partial Carries for Bit Positions 2 through 4                       | 7-8         |

| 7-3.          | Production of Final Sum Bits of 1 for Bit Posi - tions 2 through 4                                 | 7-8         |

| 7-4.          | Parity Bit Production From First Gating Network                                                    | 7-9         |

| 7-5.          | Production of Final Parity Bit                                                                     | 7-10        |

| 7-6.          | Summary of Modulo-3 Check-Bit Generation                                                           | 7-12        |

| 8-1.          | Memory-Write-Register Inputs from UNISERVO II and General-Purpose Channels, and Function           | 8-4         |

| 8-2.          | Signals                                                                                            | 8-9         |

| 8-3.          | Bit-Entry Sequence of Input Formats into  Memory-Write Register                                    | 8-10        |

| A-1.          | Figure References and Engineering Drawings for Section 2                                           | A-1         |

| A-2.          | Figure References and Engineering Drawings for Section 3                                           | A-1         |

| A-3.          | Figure References and Engineering Drawings for Section 4                                           | A-1         |

| A-4.          | Figure References and Engineering Drawings for Section 5                                           | A-1         |

| A-5.          | Figure References and Engineering Drawings for Section 6                                           | A-2         |

| A-6.          | Figure References and Engineering Drawings for Section 7                                           | A-2         |

| A-7.          | Figure References and Engineering Drawings for Section 8                                           | A-3         |

# Section 1 INTRODUCTION AND GENERAL DESCRIPTION

This manual describes the logical operation of the UNIVAC ® III Central Processor Model 121. No attempt is made to explain in complete detail the interrelation of all logic components as shown on the logic diagrams. It is assumed that the reader will be able to determine the details of the central-processor operations from the logic diagrams. In order to aid in the transition from the manual to the logic diagrams, all signal designations mentioned in the manual are presented in the same form that they appear on the logic diagrams, and appendix A lists all logic prints and the print revisions on which the information in the manual is based.

The related manuals in the UNIVAC III manual series are as follows:

Manual 2, Synchronizers for Peripheral Equipment — Logic Description

Manual 3, Logic Diagrams

Manual 4, Signal Analysis

Manual 5, Circuitry

Manual 7, Core Storage Model 122 and Model 197 — Description and Maintenance

Section 1 of manual 1 describes, in general, the major logic areas of the central processor, and section 2 describes all UNIVAC III system logic elements and assemblies. Sections 3 through 14 describe, in detail, the operation of each logic area that was introduced in section 1. The organization of the manual is planned so that the reader may, after reading sections 1 and 2, proceed to any of the twelve sections (sections 3 through 14) without the necessity of reading all sections in sequence.

Sections 1 through 8 contain the introduction to the manual and an explanation of the logic necessary

to read and index instructions. Sections 9 through 14 describe the logic necessary to execute the central-processor instructions.

#### 1-1. CENTRAL-PROCESSOR SPECIFICATIONS

The central processor performs all the data-processing functions of the UNIVAC III computing system and coordinates the operations of all input-output devices in the system. The design methods that were so successfully used in the production and maintenance of the LARC\* and other UNIVAC solid-state computing systems have been applied to the UNIVAC III central processor. Because of this experience, the UNIVAC III central processor offers features in a medium priced computing system that are normally found only in higher priced systems.

The general, programming, arithmetic, and storage specifications for the UNIVAC III central processor are as follows:

#### General

Synchronous operation

4 μsec per minor cycle 9 pulse times per minor cycle

Serial-parallel transfer

27-bit words

24 data bits, 1 sign bit, 2 check bits

Typewriter input and output

15 index registers

Automatic sequencing of memory accesses between central processor and input-output units

The following registered trademark of the Sperry Rand Corporation is used in this manual: UNIVAC.

<sup>\*</sup>Trademark of the Sperry Rand Corporation.

Programming

Single-address instructions

Stored program

61 well defined instructions in SALT code

8 programmable sense FF's

Automatic interrupt

Tested by the program

Automatic field selection

Indirect addressing

Arithmetic

Operands

6, 12, 18, or 24 decimal

digits

24, 48, 72, or 96 binary digits

4, 8, 12, or 16 alphanumeric characters

Arithmetic operations performed with either binary or decimal numbers

Storage

Expandable magneticcore memory

8192, 16,384, 24,576, or 32,768 words

#### 1-2. UNIVAC III CENTRAL-PROCESSOR LOGIC FEATURES

Some of the outstanding features of the UNIVAC III central processor are: 4-bit parallel transfer, overlapping operation, multiprecision instructions, priority, multiply instructions, initiate input-output instructions, automatic programming aids, scatterread/gather-write control, number-system compatibility, and checking features.

#### 1-3. Four-bit Parallel Transfer

All data format manipulation in the UNIVAC III central processor is performed four bits (a decimal digit) at a time, and all information is transferred within the central processor four bits at a time. The use of the decimal-digit-at-a-time transfer represents the most efficient way of handling data in a medium priced decimal computer because the decimal digit is the smallest unit of information that is normally required.

#### 1-4. Overlapping Operation

The reading of an instruction from memory and the indexing of the instruction is performed while the previous instruction is being executed. This overlapping of instructions is normally found only in the most expensive data processing systems.

#### 1-5. Multiprecision Instructions

The UNIVAC III instruction catalogue permits the programmer to designate the precision of the arithmetic operation that is to be performed. This presents two distinct advantages: one, the programmer can work directly with numbers that contain as many as 24 decimal digits or 96 binary digits without any programming manipulation; two, an arithmetic operation takes only as long to perform as is necessary. No time is wasted adding meaningless digits when they are not required by the operation. Thus, the greater precision of the long word is combined with the faster operation and economy of the short word.

#### 1-6. Priority

The UNIVAC III central processor automatically allots memory access to the central processor and to the input-output (I-O) devices in a way that makes best use of computer operating time. This is a feature that is normally found only in the most expensive computing systems.

#### 1-7. Multiply Instructions

The multiply instruction uses a special technique called short cut multiply which decreases by onethird the maximum number of additions necessary for a multiply problem.

#### 1-8. Initiate Input-Output Instruction

The instruction which initiates the input-output operations, supplies the designated input-output synchronizer with all necessary control information, and then transfers control of the input-output operation to the synchronizer. After the initiate I-O instruction has been performed, the only central processor time that is required for an input-output operation is the time necessary to transfer a word between a synchronizer and memory. Thus the highspeed central processor is not limited by the slower speed input-output devices.

#### 1-9. Automatic-Programming Aids

Automatic field selection and indirect addressing, which are invaluable aids in data processing applications, are built into the central processor. Also, the extensive use of the sense flip-flop and automatic-interrupt features provide the programmer and the operator with maximum control over the system.

## 1-10. Scatter-Read/Gather-Write Control Word

The use of the scatter-read/gather-write control word allows one central-processor instruction to control the transfer of data between magnetic tape and various segments of memory. This transfer is done by the automatic reading of sequential scatter-read/gather-write control words from memory. These control words contain the address of the first memory location of a memory segment and the number of words in that segment. When the data from one segment are processed, the next scatter-read/gather-write control word is automatically read from memory. Thus, information can be transferred between a tape unit and various segments of memory with one central-processor instruction. This represents a great saving in program time.

#### 1-11. Number-System Compatibility

The central processor performs arithmetic operations with either binary or decimal numbers.

#### 1-12. Checking Features

All transfers between the central processor and memory are checked both for correct transfer and for address decoding. Also, all addition and subtraction operations are automatically checked.

# 1-13. FUNCTIONAL COMPONENTS OF CENTRAL PROCESSOR

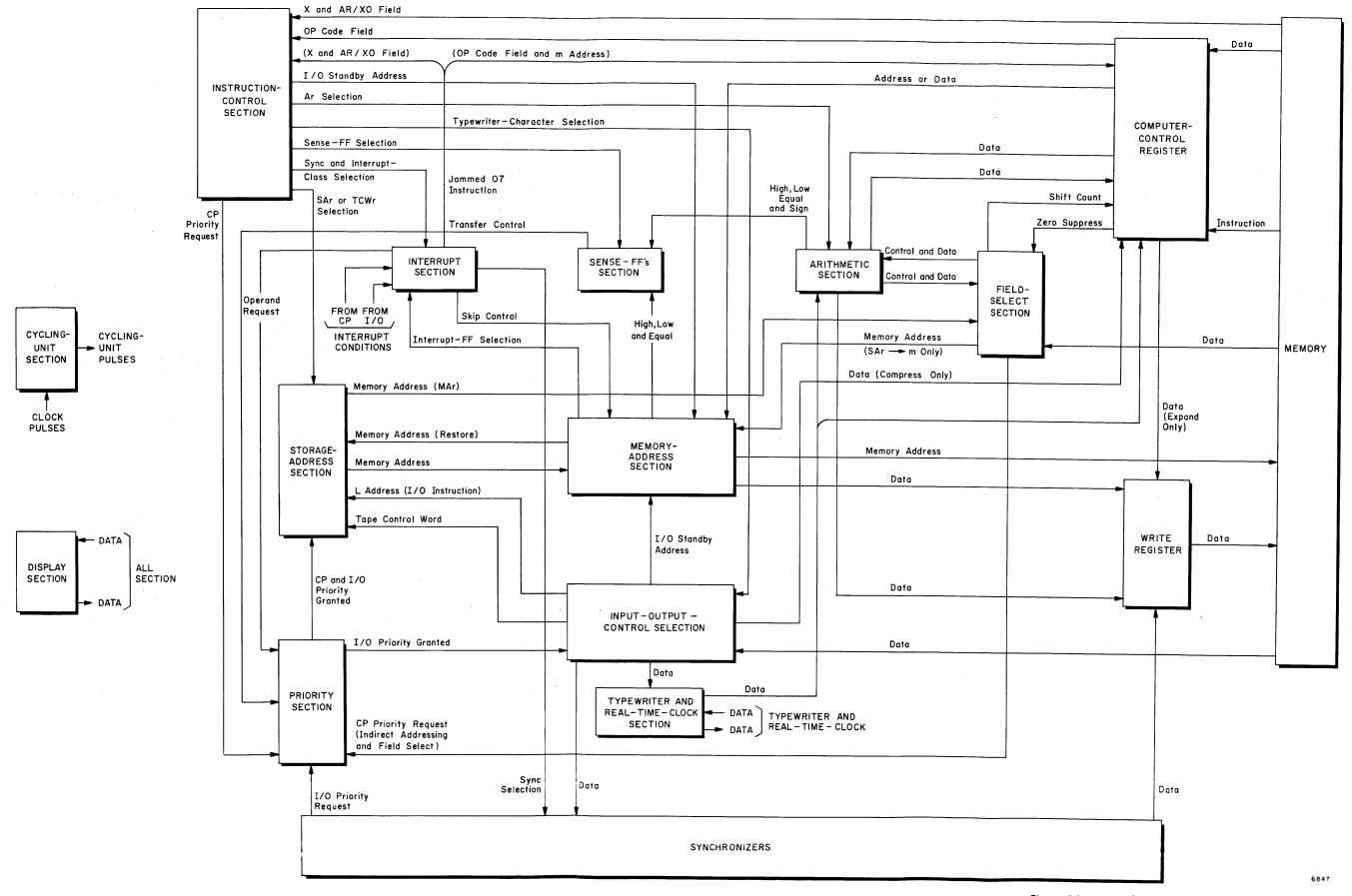

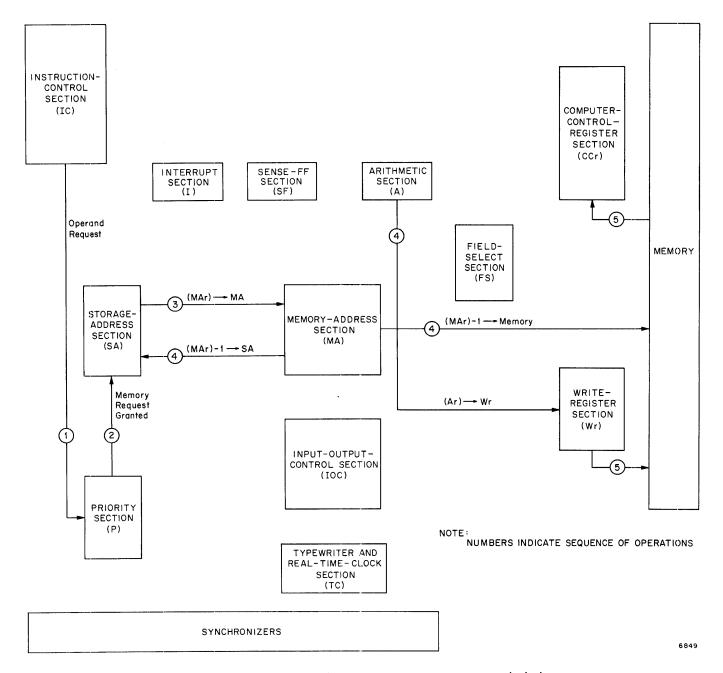

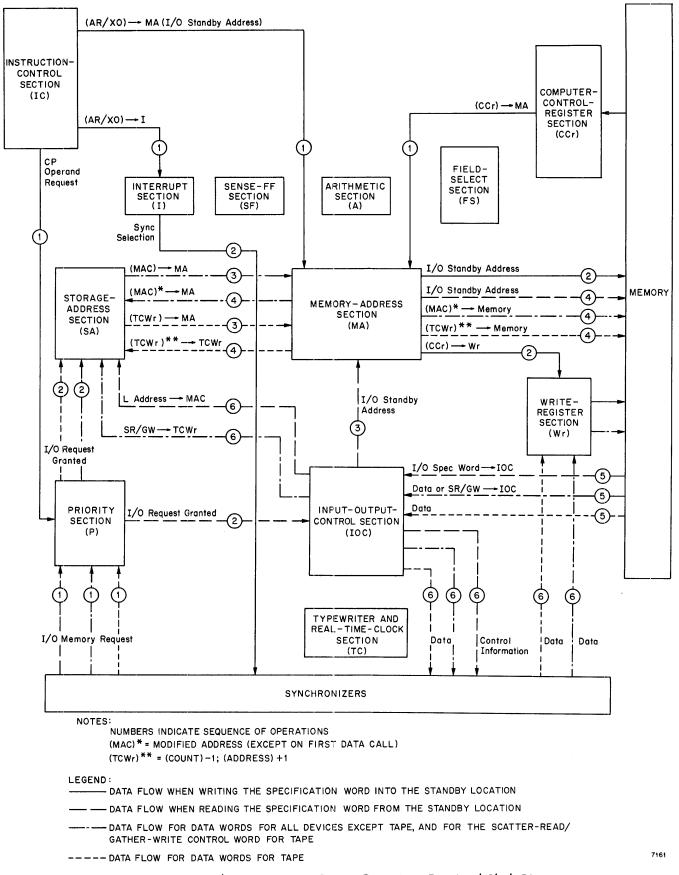

Figure 1-1 shows the functional components of the central processor and the major data-flow paths between these components. The purpose of each functional component will be explained in the text that follows; the data flow will be explained later in this section (heading 1-32).

#### 1-14. Computer-Control Register

The computer-control register (CCr) is the main working register in the central processor. This register performs all the shifting and data manipulation that is required by the central processor. The CCr also receives all the memory inputs which contain central-processor data or instructions.

#### 1-15. Instruction-Control Section

The instruction-control section receives each central-processor instruction, partly from memory and partly from the CCr, and then decodes these instructions into various instruction lines, program counts, and register selection outputs as specified by the instruction. These signals then are used by other sections of the central processor to control the execution of the instruction.

#### 1-16. Storage-Address Section

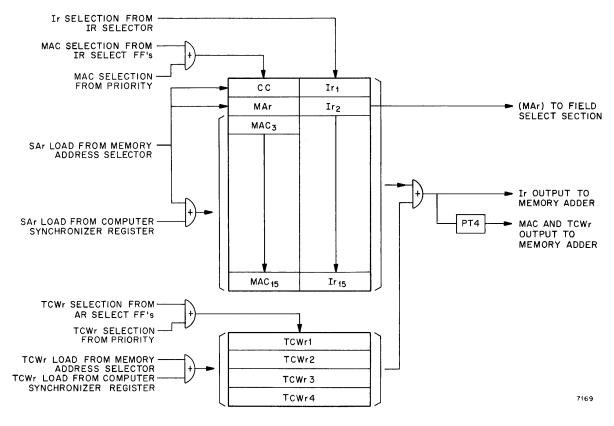

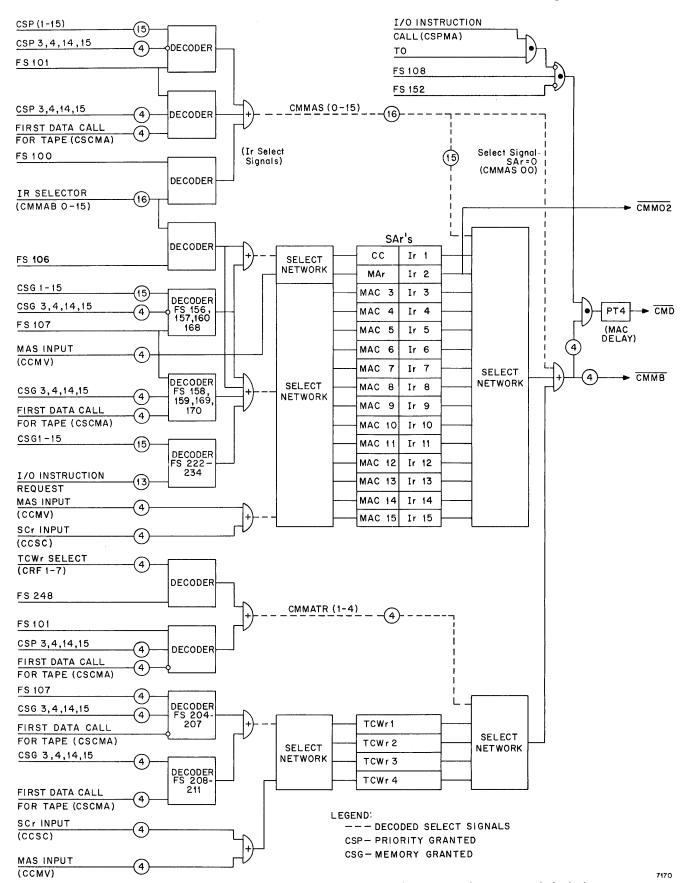

The storage-address section contains a maximum of 30 storage-address registers (SAr). These registers include a maximum of 15 index registers (Ir) which are used to modify the instruction address; and a maximum of 15-memory-address counters (MAC), which contain input-output memory addresses, an instruction memory address, and an operand memory address. The MAC that contains the instruction memory address is called the control counter (CC), and it stores the address of the last instruction that was read from memory. The address of the last operand that was read from memory is stored in the MAC called the memory-address register (MAr). All other MAC's contain memoryaddress information for input-output operations. There is one MAC for each input-output operation and one MAC for each input-output channel.

The MAC's and Ir's contain 15 bits each; correspondingly numbered MAC's and Ir's occupy one 36-bit register (6 bits of this register are not used).

In addition to the storage-address registers, the storage-address section also contains four 24-bit tape-control-word registers (TCWr) which hold control and address information for tape operations, and which occupy one 36-bit register each.

#### 1-17. Field-Select Section

The field-select section, which contains 10 flip-flops and control logic, performs the following functions in the central processor:

Provides signals that control field selection or indirect addressing;

Provides a path for memory-address information during the transfer of the contents of a SAr or a TCWr to memory;

Provides temporary storage of arithmetic-carry information during multiprecision operations;

Provides a means of deleting zeros and commas during zero-suppress operations;

Stores and modifies the shift count; and

Provides a means of shifting during multiply and divide operations.

#### 1-18. Memory-Address Section

The memory-address section performs all memory-address modification and supplies addresses to memory for both read and write operations. The section contains an adder and a register. The adder, called the memory adder, performs all address modification, provides a transfer path for storing data during certain instructions, and provides a means of comparing data during other instructions. The register, called the memory-address selector (MAS), converts the address format from serial to parallel, supplies an address to memory, and provides a path for loading either the SAr's or the TCWr's.

#### 1-19. Arithmetic Section

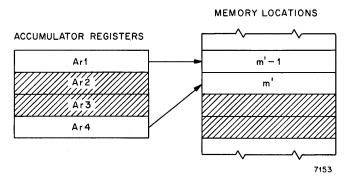

The arithmetic section performs all the arithmetic operations and the data modification for the central processor and provides temporary storage for information. The arithmetic section contains four accumulator registers (Ar1 through Ar4) and an adder (called the main adder). The accumulator registers are addressed either singly or in combination. When addressed, they supply one word at a time to either the write register for storage into memory, or to the computer-control register for data manipupation, or to the main adder for modification.

When more than one Ar is addressed, the register designated by the smaller number contains the most significant digits, and the register designated by the larger number contains the least significant digits. For example, if Ar1 and Ar4 are designated, Ar1 contains the most significant digits, and Ar4 contains the least significant digits.

The main adder performs the addition process for all arithmetic instructions. Besides its function in the arithmetic instructions, the main adder is used in logical operation instructions (erase and superimpose), is used in comparison instructions, and is the only input path to the Ar's. In all these uses the main adder performs the addition process; the different results are achieved by varying the inputs to the adder.

#### 1-20. Input-Output Control Section

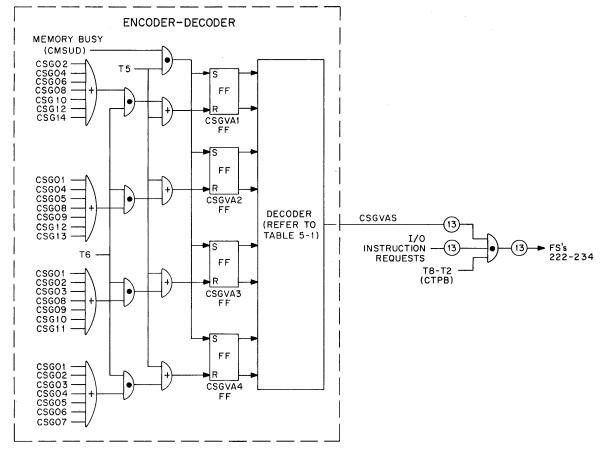

The input-output control section coordinates data transfer between memory and the synchronizers, and checks all data transfers between memory and the central processor. The section contains one register, the synchronizer-control register (SCr), which provides temporary storage for all information that is read from memory. Control logic in the section checks data transfers, arranges data in the SCr into the input-output formats, and coordinates the input-output operations.

#### 1-21. Priority Section

The priority section receives memory requests from the central processor and from the various inputoutput synchronizers and allots memory access according to a predetermined sequence. The outputs from the priority section control the reading and restoring of memory addresses in the storageaddress section. The priority-section outputs are also encoded to produce an address during inputoutput operations.

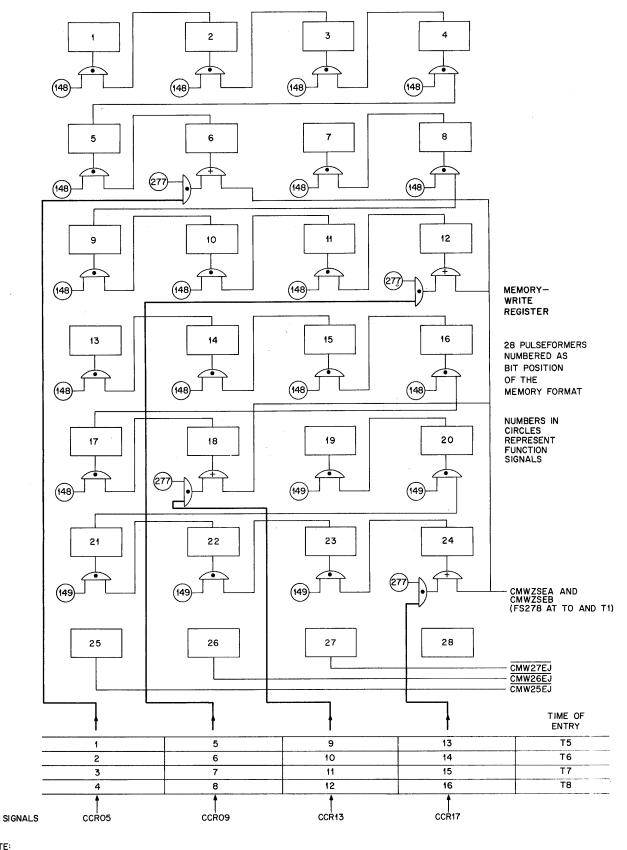

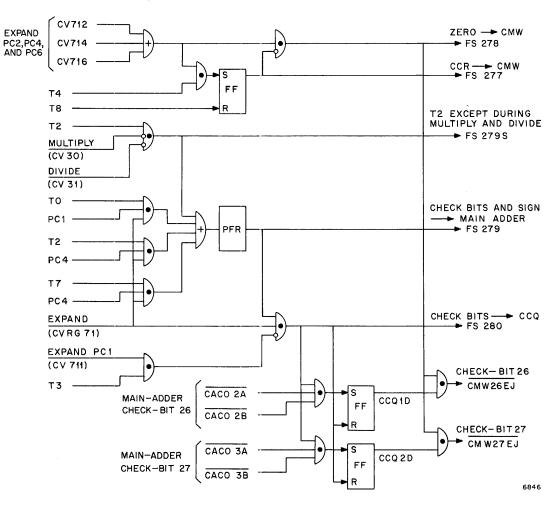

#### 1-22. Write Register

The write register supplies data to memory during all store operations. The register receives data in different formats from the arithmetic section, the synchronizers, the memory-address section, and the computer-control register. The write register then arranges these formats into the memory format and supplies the data to memory.

#### 1-23. Sense-Flip-Flop Section

The sense-FF section contains eight sense FF's and an inhibit-input-output-interrupt FF, all of which are set, reset, or tested by an instruction; and three comparison FF's, which represent equal to, greater than, or less than conditions. The appropriate high, low, or equal flip-flop is set during specific instructions if the minuend input is either equal to, greater than, or less than the subtrahend input. The comparisons are made either in the memory adder or the main adder. All the flip-flops in the sense-FF section can be tested by an instruction. If the flip-flop is set when tested, program control is transferred to a subroutine.

#### 1-24. Interrupt Section

The interrupt section receives inputs from the central processor and the synchronizers, and it interrupts the program when there are certain predetermined conditions. When the program is interrupted,

Figure 1-1. Central Processor, Functional Block Diagram

a transfer instruction is jammed into the CCr and into the instruction-control section. This instruction is then executed.

### 1-25. Typewriter and Real-Time-Clock Section

The typewriter and real-time-clock section controls all data transfers between the central processor and either the typewriter or the real-time clock. The section contains a 6-bit buffer register which stores one character at a time; a translator, which translates the 6-bit character into typewriter code; and control logic.

#### 1-26. Cycling-Unit Section and Display Section

The cycling unit supplies all sections of the central processor with timing signals. These signals are produced and controlled by the central clock. The display section contains control logic which lights the indicators on the engineer's console and which permits the manual control of computer operations from the engineer's console.

#### 1-27. UNIVAC III WORD FORMATS

There are four types of word formats used in the UNIVAC III central processor. These types are as follows:

Data words, which represent three types of data;

Instruction words, which represent all instructions;

Input-output specification words, which control the operation of the input-output devices; and

Control words, which perform special functions during specific instructions.

All word formats contain check bits in bit-positions 26 and 27. These check bits are not included in the descriptions that follow.

#### 1-28. Data Words

There are three types of data words: the decimal data word, the alphanumeric data word, and the binary data word.

The format of the decimal data word is as follows:

| 25 | 24    | 21 | 20    | 17 | 16    | 13 | 12    | 9 | 8     | 5 | 4     | 1_ |

|----|-------|----|-------|----|-------|----|-------|---|-------|---|-------|----|

| s  | DIGIT | 6  | DIGIT | 5  | DIGIT | 4  | DIGIT | 3 | DIGIT | 2 | DIGIT | 1  |

#### where

DIGIT (1 through 6) represents six decimal digits in XS-3 code.

S represents the sign bit (0 for positive, 1 for negative).

The format of the alphanumeric data word is as follows:

| 25 | 24    | 19 | 18    | 13 | 12      | 7 | 6     | 1 |

|----|-------|----|-------|----|---------|---|-------|---|

| s  | CHARC | 4  | CHARC | 3  | CHARC 2 |   | CHARC | 1 |

#### where

CHARC (1 through 4) represents four alphanumeric characters.

S is the same as in the decimal data word.

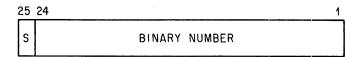

The format of the binary data word is as follows:

#### where

BINARY NUMBER represents one 24-bit binary number.

S is the same as in the decimal data word.

#### 1-29. Instruction Word

There is one general instruction word which is used for all instructions.

The format of the instruction word is as follows:

| 25 24      | 21 20 | 15 '    | 14 11    | 10 | 1       |

|------------|-------|---------|----------|----|---------|

| IA<br>FS X |       | OP CODE | AR<br>XO | m  | ADDRESS |

#### where

m ADDRESS represents the first ten bits (unmodified) of a memory address; a shift count; or an interrupt FF. (The unmodified address is referred to as the m address and the modified address is referred to as the m' address. The contents of the m-ADDRESS field are automatically modified by the contents of the index register specified by the contents of the X-field.)

#### Introduction and General Description

#### AR/XO represents the following:

The precision of an arithmetic operation, and the Ar's specified in instructions that use Ar's;

The sense FF that is to be addressed during a sense-FF instruction;

The SAr designated during an SAr-load or -store instruction:

The TCWr that is specified during a TCWr-store instruction:

The type of interrupt FF specified during a test, or reset interrupt-FF instruction; or

The synchronizer and standby location to be used during an initiate I-O instruction.

OP CODE is the octal representation of the instruction to be performed. X represents the index register which modified the m-ADDRESS field. IA/FS represents the indirect-addressing or field-selection control bit.

#### 1-30. Input-Output Specification Words

Bit positions 1 through 15 of the input-output specification word contain the L address which is the address of the first data word, and bit positions 17 through 24 contain information which controls the operation of the synchronizer. The specific function performed by the contents of bit positions 17 through 24 varies with each input-output unit and these functions are described in the synchronizer manuals.

Bit position 16 of the I-O specification word causes a program interrupt if it contains a 1-bit.

#### 1-31. Control Words

The four types of control words are as follows:

Indirect-addressing control word, which specifies the address of the next operand during indirect addressing;

Field-selection control word, which specifies the address of an operand and selects a specified field within that operand;

Index-register-modification control word, which specifies the number with which an index register is to be modified and compared; and

Scatter-read/gather-write control word, which specifies the address of the first data word and

the number of words to be transferred during a tape operation.

The format of the indirect-addressing control word is as follows:

| 25 24    | 21 | 20 18 17 | 16 15 |           | 1 |

|----------|----|----------|-------|-----------|---|

| IA<br>FS | Х  | 0 0 0    |       | L ADDRESS |   |

#### where

L ADDRESS represents the address of the next operand. (This address is indexable.)

Bits 18 through 20 must be all 0's.

X represents the index register which modifies the L ADDRESS field.

IA/FS represents the field-selection or indirect-addressing control bit.

The format for the field-selection control word is as follows:

| 25 24 | 1 21 | 20 16 | 15 11 | 10 1      |

|-------|------|-------|-------|-----------|

| 0     | Х    | LBB   | RBB   | m ADDRESS |

#### where

m ADDRESS represents the least significant 10 bits (unmodified) of the next operand address.

RBB (right-boundary bit) represents the bit position of the least-significant bit (LSB) of the field that is selected.

LBB (left-boundary bit) represents the bit position of the most-significant bit (MSB) of the field that is selected.

X represents the index register which modifies the m address.

Bit 25 must be a 0.

The format for the index-register-modification control word is as follows:

| 25 | 24 10 | 9 1 |

|----|-------|-----|

| *  | CA    | MA  |

where

MA represents the amount by which the index register is modified (increased or decreased).

CA represents the number with which the modified index register is compared.

(\*If bit position 25 contains a 0, the contents of the MA-field is added to the contents of the Ir; if bit position 25 contains a 1, the MA-field is subtracted.)

The format for the scatter-read/gather-write control word is as follows:

| 25 | 24 16 | 15 1      |

|----|-------|-----------|

| *  | COUNT | L ADDRESS |

#### where

L ADDRESS represents the address of the first data word. (This address is not indexable.)

COUNT represents the number of words to be processed.

(\*If bit 25 is a 1, it means that this is the last scatter-read/gather-writer control word, and bits 1 through 24 are ignored.)

## 1-32. DATA FLOW IN THE UNIVAC III CENTRAL PROCESSOR

The major data flow in the central processor is as follows:

Data flow during an instruction call (when an instruction is read from memory);

Data flow during multiprecision instructions:

Data flow during instructions which use the main adder;

Data flow during instructions which transfer data between the SAr and memory;

Data flow during shift instructions;

Data flow during miscellaneous instructions such as transfers, sense-FF instructions, expand instructions, and zero-suppress instructions; and

Data flow during the input-output operations.

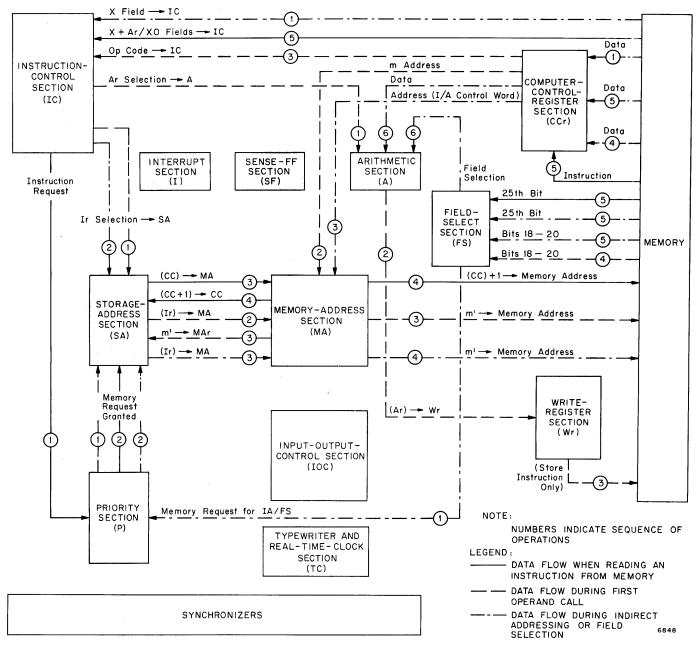

#### 1-33. Data Flow During an Instruction Call

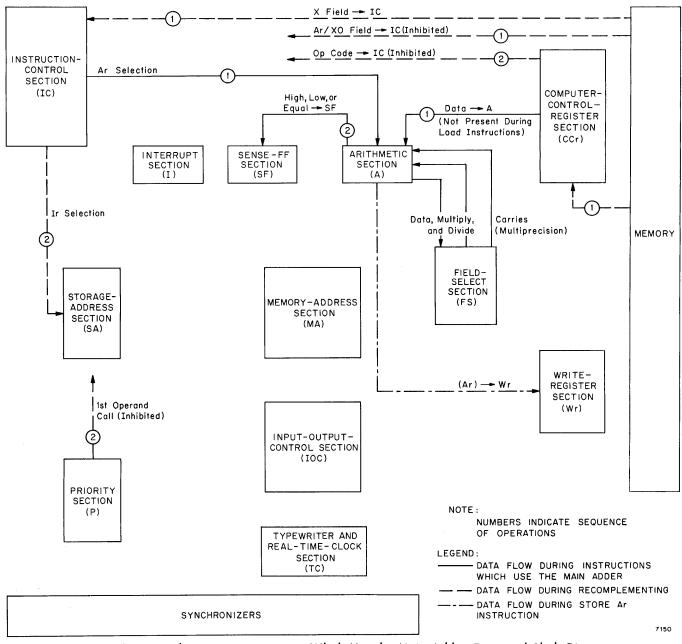

The data flow during an instruction call (figure 1-2) is divided into three parts: the reading of the in-

struction from memory; the reading of the first operand from memory, called the first operand call; and the performance of field selection or indirect addressing. The first two parts are performed for all instructions, and the third part is performed only when specified by a 1 in the 25th bit position of the instruction word.

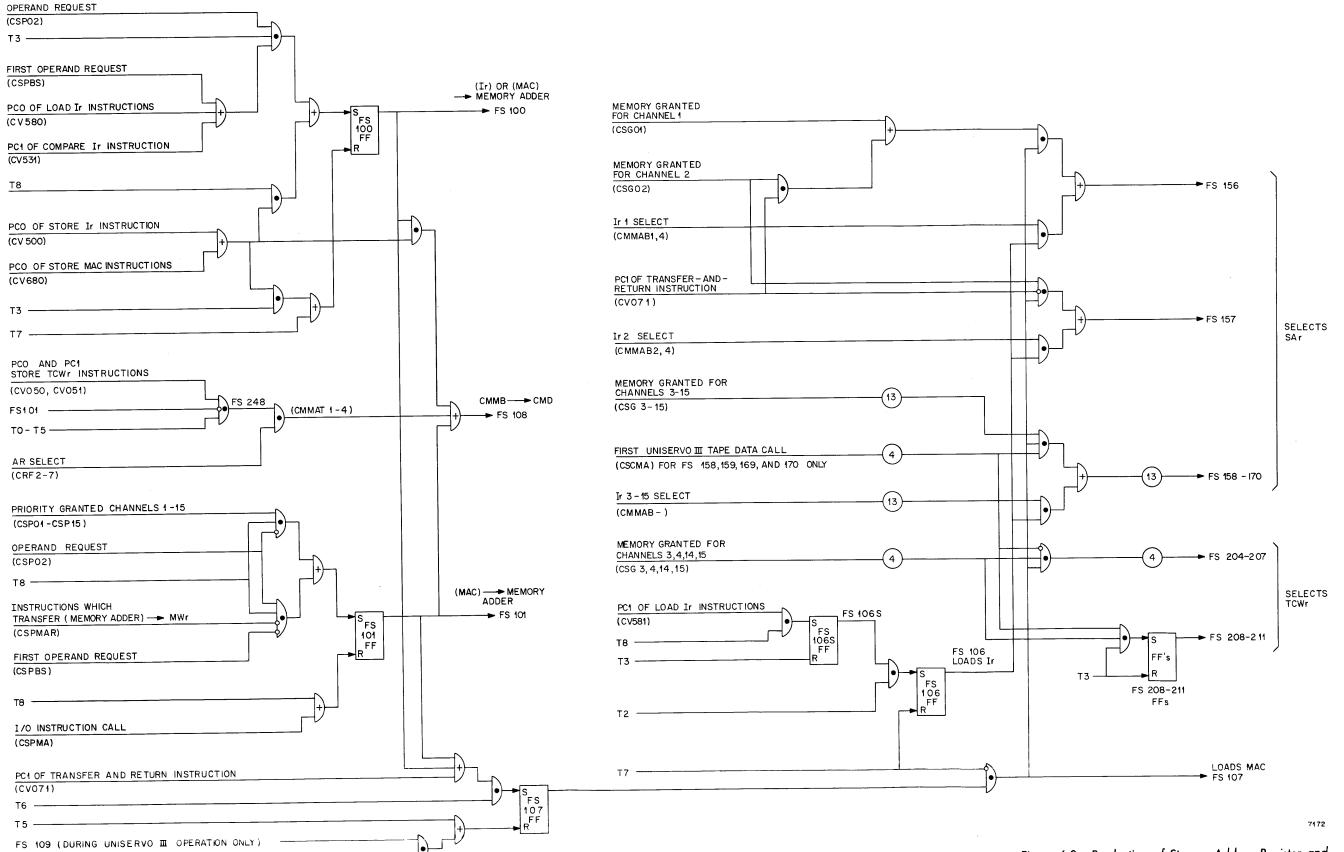

1-34. DATA FLOW WHEN READING THE INSTRUC-TION FROM MEMORY. A memory request for an instruction is produced at the end of the previous instruction by the instruction-control section. The request is routed to the priority section where memory access is granted. When memory access is granted, the contents of the CC (in the storageaddress section) are transferred to the adder in the memory-address section where they are increased by 1. The contents of the CC-plus-1 are then sent to the memory-address selector, and from there to memory. The location specified by the contents of CC-plus-1 contains the next instruction. When the instruction is read from memory, the X- and AR/ XO-fields are read directly into the instructioncontrol section and the complete instruction word is read into the CCr.

1-35. DATA FLOW DURING THE FIRST OPERAND CALL. The contents of the X- and AR/XO-fields are decoded by the instruction-control section. The X-field selects an index register and the AR/XO-field selects an accumulator register. The contents of the selected Ir and the maddress from the CCr then are added in the memory adder. At this time, the operation code is read from the CCr to the instruction-control section. As a result of this decoding process, the index-register and accumulator-register selections are made before the operation code is decoded.

The m' address is sent to the MAS and, from there, to memory and to MAr. Also, the contents of the specified Ar are sent to the write register at this time. If the instruction is a store instruction, the contents of the write register are written into memory. Otherwise, the contents of the memory location specified by the m' address are read into the CCr. Many instructions do not require an operand. In these cases, the CCr is cleared during the next minor cycle.

The 25th-bit position of the instruction is transferred into the field-select section. If the 25th-bit position contains a 1 bit, the first operand is either an indirect-addressing or field-selection control word.

1-36. DATA FLOW DURING FIELD SELECTION AND INDIRECT ADDRESSING. If an indirect-addressing or field-selection control word is specified by a 1 bit in the 25th-bit position of the instruction word, the contents of the X-field of the control

Figure 1-2. Data Flow During an Instruction Call, Functional Block Diagram

word (which is the first operand) is read into the instruction-control section at the same time that the control word is read into the CCr. The contents of the Ir selected by the X-field then modifies the address field of the control word in the same way as in the first operand call. The operand specified by the new m' address then is read into the CCr.

When the first operand is read into the CCr, bits 18, 19, and 20 are also read into the field-select section. If these bit positions do not contain all 0's, the contents of the operand specified by the new m' address (second operand) are transferred to the arithmetic section and only the fields selected by the field-selection control word are transferred to

the specified Ar. If bit positions 18, 19, and 20 contain all 0's and bit position 25 does not contain a 1 bit, all bits in the second operand are processed. If bit-position 25 contains a 1, however, the operand is treated as another indirect-addressing or field-selection control word.

#### NOTE

In all data-flow descriptions that follow, the description begins at the conclusion of the first operand call.

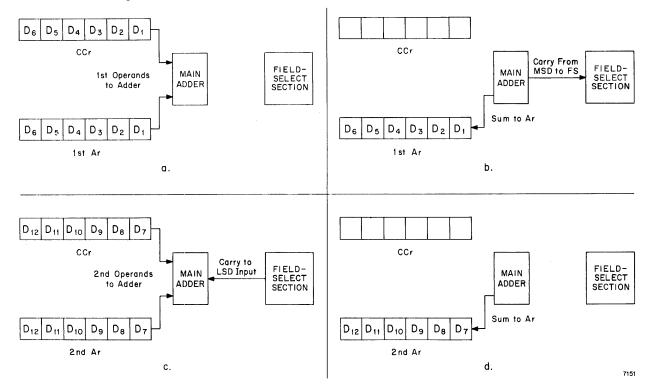

# 1-37. Data Flow During Multiprecision Instructions

During multiprecision instructions, an operand request is produced by the instruction-control section (figure 1-3) for each additional operand. When this request is granted, the contents of MAr are transferred to the memory-address section where they are decreased by 1. This modified address is then transferred to memory and also back to the MAr. The contents of the memory location, represented by the modified address, are read from memory into CCr during a read operation, or the contents

of the write register are written into the memory location during a write operation.

## 1-38. Data Flow During Instructions Which Use the Main Adder

The data flow is similar for all instructions which use the main adder. These instructions include the add, subtract, compare, logical operations, and extract instructions (figure 1-4). The operand in the CCr is transferred to the arithmetic section and is combined with the contents of the specified accumulator registers. The specific differences among

Figure 1-3. Data Flow During Multiprecision Instructions, Functional Block Diagram

Figure 1-4. Data Flow During Instructions Which Use the Main Adder, Functional Block Diagram

instructions are produced through different methods of gating the operands into the main adder. During these instructions, the memory request for the next instruction is made while the last operand is being read into the arithmetic section.

When multiprecision arithmetic operations are specified, the word containing the least significant bits is transferred to the main adder first, and the word containing the most significant bits is transferred last. The carry from the most-significant-bit position of one word is stored in the field-select section during a multiprecision operation. The carry is then supplied to the least-significant-bit position of the next word (figure 1-5).

1-39. RECOMPLEMENTING. The result of the add or subtract instructions may produce a negative answer. If the answer is negative, it is expressed in complement form and must be recomplemented. Recomplementing is performed after the addition of the last operand, and after the next instruction is read from memory into the CCr. During the time that the recomplementing is performed, the next instruction is held in the CCr until the recomplementing is completed. The contents of the X-field of the next instruction, however, are transferred to the instruction-control section, the index register is selected, and the memory request for the operand is made. When recomplementing is completed, the memory request is granted. The contents of the

Figure 1-5. Example of Double-Precision Add with Carries, Functional Block Diagram

operation-code field and the AR/XO-field then are transferred to the instruction-control section, and the first operand is read from memory.

1-40. HIGH, LOW, AND EQUAL FLIP-FLOPS. During the add, subtract, and compare instructions, there is an output from the arithmetic section which sets flip-flops in the sense-FF section. The add and subtract instructions set the equal FF if the result equals zero, and reset it if the result does not equal zero. The compare instructions set the appropriate flip-flop (high, low, or equal).

1-41. EXTRACT INSTRUCTIONS. The contents of the fields to be extracted during an extract instruction are determined by the field-select FF's in the same way that the fields are determined during field selection. Therefore, field selection must be designated for an extract instruction; otherwise, the extract instruction will function in the same way as a load-Ar instruction.

1-42. MULTIPLY AND DIVIDE INSTRUCTIONS. The multiply and divide instructions are done by successive additions and subtractions. The 48-bit dividend occupies Ar1 and Ar2 and the divisor is contained in the CCr. The quotient is placed in Ar2 and the remainder is placed in Ar1. The multiplier occupies Ar1 and the multiplicand is contained in the CCr; the 48-bit product is placed in Ar2 and Ar3. Shifting in both the multiply and divide operations is done by routing the data through the field-select section.

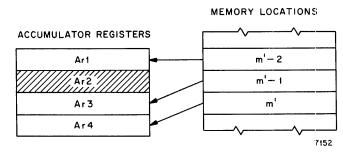

1-43. STORE- AND LOAD-ACCUMULATOR IN-STRUCTIONS. During the execution of the accumulator store instruction, data are transferred from the specified Ar's directly to the write register, and from there into memory. During the execution of the multiword load instructions, the contents of adjacent memory locations may be transferred to any designated set of Ar's. During the execution of the multiword store instructions, the contents of any set of Ar's can be transferred to adjacent memory locations. The only restriction is that the contents of the lowest numbered Ar occupy the last memory location during a store instruction and that the lowest numbered Ar receives the input from the last memory location during a load instruction.

Figure 1-6 shows the storing of three words from adjacent memory locations into three non-adjacent Ar's, and figure 1-7 shows the storing of the contents of two Ar's in adjacent memory locations.

Figure 1-6. Loading Accumulator Registers from Adjacent Memory Locations, Diagram

Figure 1-7. Storing Contents of Accumulator into Adjacent Memory Locations, Diagram

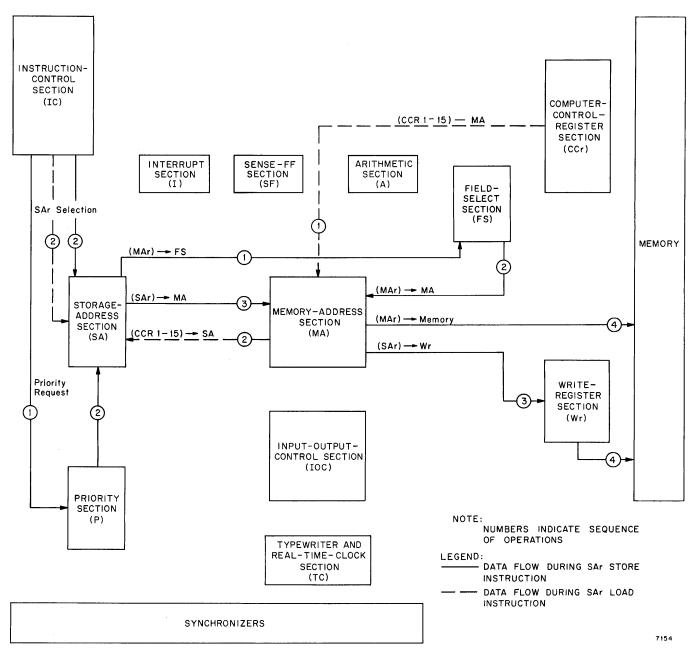

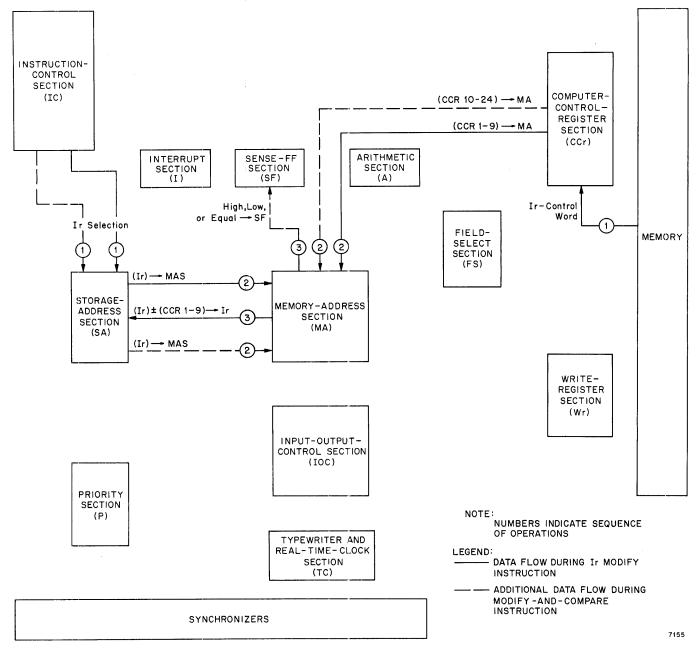

#### 1-44. Data Flow During Instructions Which Transfer Data Between the Storage-Address Registers and Memory

The instructions which transfer data between the storage-address registers and memory are these:

Instructions which store the contents of a SAr (figure 1-8);

Instructions which load a SAr from memory (figure 1-8); and

Instructions which either modify, or modify and compare the contents of an Ir (figure 1-9).

Figure 1-8. Data Flow During Storage-Address-Register Load and Store Instructions, Functional Block Diagram

Figure 1-9. Data Flow During Index-Register Modify and Compare Instructions, Functional Block Diagram

1-45. DATA FLOW DURING INSTRUCTIONS WHICH STORE THE CONTENTS OF A STORAGE-ADDRESS REGISTER. When the first operand is read from memory during a store-SAr instruction, another memory request is made. When memory access is granted, the contents of the SAr specified by the AR/XO-field of the instruction are transferred through the memory adder to the write register. The m¹ address is sent from MAr through the field-select section to the MAS. The contents of the MWr, which contain the contents of the SAr, then are transferred to the memory location specified by the MAr.

1-46. DATA FLOW DURING INSTRUCTIONS WHICH LOAD A STORAGE-ADDRESS REGISTER. During

the execution of the load-SAr instructions, the first 15 bits of the operand in the CCr are transferred through the memory-address section to the SAr specified by the instruction-control section. The request for the next instruction is made while data are being transferred to the register.

1-47. DATA FLOW DURING INSTRUCTIONS WHICH MODIFY AND COMPARE THE CONTENTS OF AN INDEX REGISTER. For instructions which either modify, or modify and compare the contents of an Ir, the first operand is the index-register-modification control word. The contents of bit positions 1 through 9 of this word are transferred to the memory adder where they are added to or subtracted from the con-

tents of the Ir specified by the AR/XO-field of the instruction. The modified contents of the Ir are then returned to the same Ir.

If the instruction calls for a comparison, the clearing of the CCr is inhibited and the contents of the CA-field of the control word are then subtracted from the modified contents of the Ir. The result of the subtraction sets the appropriate high, low, or equal indicator in the sense-FF section.

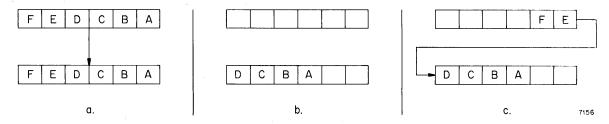

#### 1-48. Data Flow During Shift Instructions

During the execution of the shift instruction, the shift count, which is contained in the four least significant bits of the contents of the MAr, is transferred to the field-select section after the m' address has been placed in the MAr. The contents of the Ar's specified by the AR/XO-field are then transferred to the CCr. The contents of the CCr are shifted according to the type of shift instruction and then returned to the Ar's. The shifting is terminated by an end-of-shift signal from the field-select section.

The CCr performs only right decimal shifts (four bits at a time) and right binary shifts. Thus, all shifting must be performed by combinations of the two types of right shifts. Alphanumeric shifts are performed by combining decimal shifts and binary shifts. Left shifts are performed by translating the left shift counts into right shift counts.

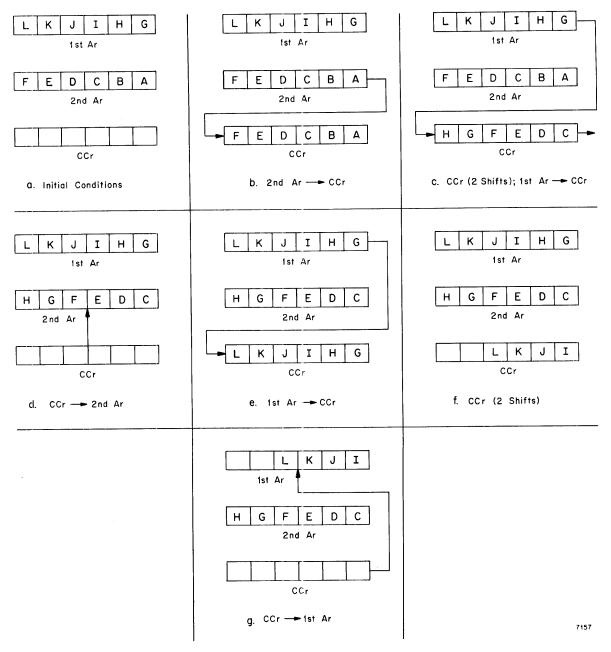

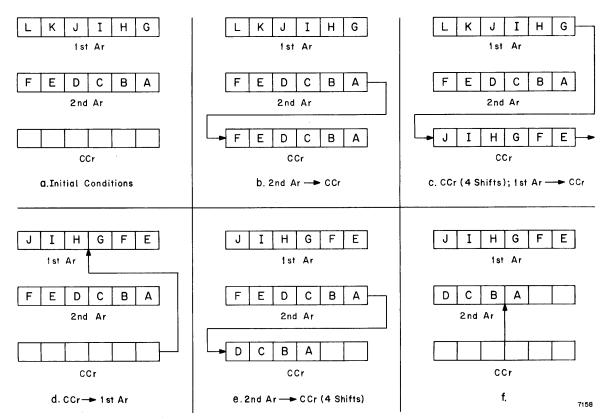

For example, the 2-digit left shift of the six digits represented by A through F in figure 1-10 could be done by either of two methods. The first method would consist of transferring all the digits from one register to another register and then performing a 2-digit left shift (a and b of figure 1-10). The second method would consist of shifting one digit at a time from the four least-significant-bit positions of one register into the four most-significant-bit positions of another register, and repeating this shifting four times (c of figure 1-10). The latter method performs the left shift by using the right-shift operation and is the method used in the UNIVAC III system.

Figure 1-11 shows the data flow for shifting right two digit positions, and figure 1-12 shows the data

flow for shifting left two digits during double-precision shift instructions. The data flow for single-precision shift instructions is shown in e, f, and g of figure 1-11 and in e and f of figure 1-12. The letters A through L represent 4-bit decimal digits.

### 1-49. Data Flow During Miscellaneous Instructions

The miscellaneous instructions are these:

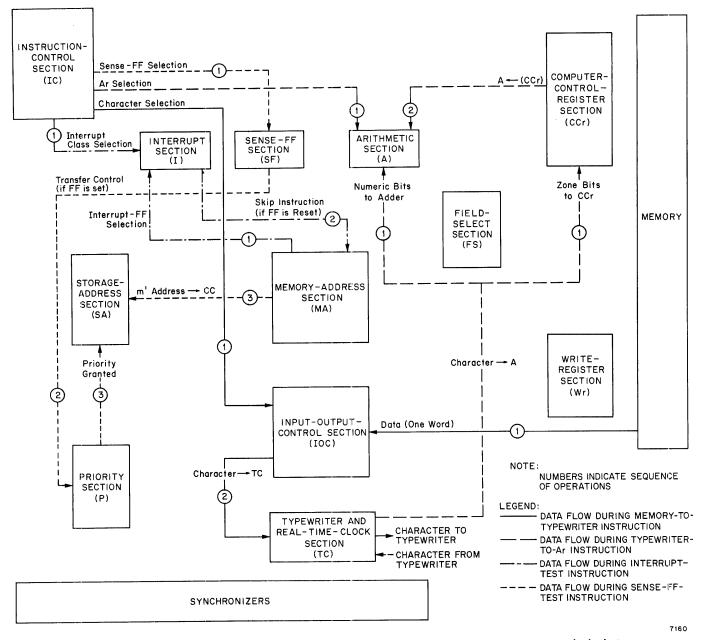

The sense-FF instructions (figure 1-13);

The test-interrupt instructions (figure 1-13);

The expand instruction (figure 1-14);

The compress instruction (figure 1-14);

The transfer instructions;

The zero-suppress instruction; and

The typewriter instructions (figure 1-13).

1-50. SENSE-FLIP-FLOP INSTRUCTIONS. The sense-FF instructions include all instructions which set, reset or test the flip-flops in the sense-FF section. A specific flip-flop is selected by the decoded output of the AR/XO-field. If the instruction requires testing the flip-flop output, and if the flip-flop is set, the m' address is placed in the CC rather than in the MAr. This transfer which is controlled from the priority section, causes the program to jump to the instruction in the location specified by the address of the test instruction.

1-51. INTERRUPT INSTRUCTIONS. During the execution of an instruction which tests or resets the interrupt FF's, the specific flip-flop is addressed through a combination of the AR/XO-field and the m-ADDRESS field. The AR/XO-field specifies a class-1 or -2 interrupt, or a priority channel in a class-3 interrupt; the m-ADDRESS field specifies the specific flip-flop. If the instruction calls for testing the flip-flop, and if the flip-flop is set, the next sequential instruction is performed; if the flip-flop is reset, 2 is added to the contents of the CC when the next instruction is read from memory. Thus, one instruction is skipped if the flip-flop is reset.

Figure 1-10. Shifting Right with Right Shifts or with Left Shifts, Diagram

Figure 1-11. Data Flow During Double-Precision Two-Digit Right Shift, Diagram

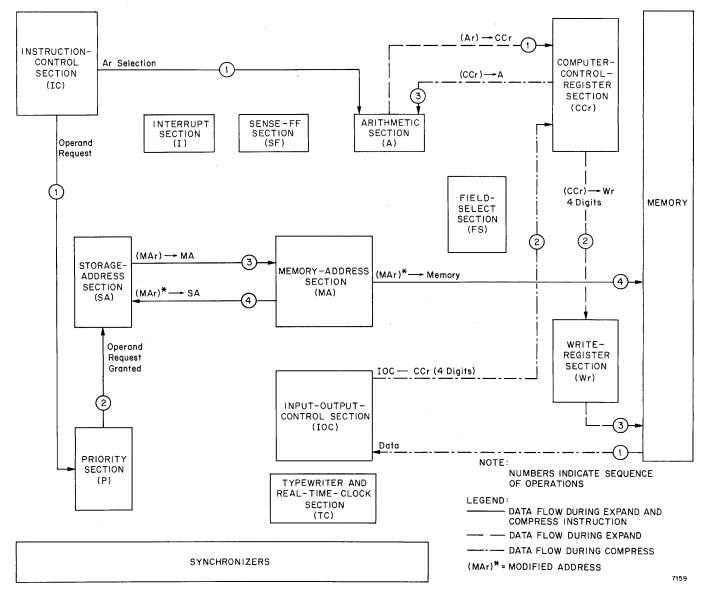

1-52. DATA FLOW DURING THE EXPAND IN-STRUCTION. The expand instruction converts 12 4-bit decimal digits (2 words contained in the Ar's) into 12 6-bit alphanumeric characters which are stored in 3 words in memory. When memory access is granted, the first word to be converted is transferred from the specified Ar to the CCr, and a memory request is made in order to write a word into memory. When memory access is granted, the first four digits of the first word are transferred to the write register where the two zone bits are added. The word then is written into the memory location specified by the address in MAr. For the storing of subsequent words, a new memory request

is made and the process is repeated. The contents of MAr are decreased by 1 after the first word is read from memory.

Three memory request are made during the expand instruction; the first to store the first four digits of the first decimal word; the second to store the last two digits of the first decimal word and the first two digits of the second decimal word; and the third to store the last four digits of the second decimal word.

1-53. DATA FLOW DURING A COMPRESS INSTRUCTION. The compress instruction reads

#### Introduction and General Description

Figure 1-12. Data Flow During Double-Precision Two-Digit Left Shift, Diagram

three alphanumeric words from memory, converts these into two decimal data words, and transfers the two words to two Ar's. The word to be compressed is transferred from memory to the input-output control section, and only the numeric bits are transferred from the input-output control section to the CCr. The data are then transferred from the CCr to the Ar's specified by the AR/XO-field of the instruction.

Three memory accesses are required for the compress instruction. During the execution of the first memory access, the first alphanumeric word is read from memory and the four digits are read into the first four digit positions of the first Ar. During the execution of the second memory access the second alphanumeric word is read from memory and the four decimal digits are transferred to the fifth- and sixth-digit position of the first Ar and to the first- and second-digit position of the second Ar. During the execution of the third memory access, the third alphanumeric word is read from memory and the four decimal digits are transferred to the last four-digit positions in the second Ar.

1-54. DATA FLOW DURING TRANSFER INSTRUCTIONS. The transfer instructions cause the program to execute the instruction contained in the m' address location rather than the next sequential instruction in the program. This is done by decoding

the first operand as an instruction and storing the m' address in the CC rather than the MAr.

1-55. DATA FLOW DURING ZERO-SUPPRESS IN-STRUCTION. During the execution of the zero-suppress instruction, the output of the CCr is decoded to produce signals which represent decimal 0's or commas. These signals then are transferred to the field-select section which uses the same process to eliminate the zeros as is used in selecting the fields during field selection. This process is continued until all leading zeros (0's to the left of the most significant digit) are removed. The unique feature of the zero-suppress instruction is that the m' address is increased, rather than decreased, with additional operand calls. This is necessary because the most-significant-digit positions must be sampled first to eliminate the leading zeros.

1-56. DATA FLOW DURING TYPEWRITER INSTRUCTIONS. During the execution of the instructions which transfer one alphanumeric character from memory to the typewriter, the word containing the character is transferred to the input-output control section. One character, which is designated by the AR/XO-field, is transferred from the input-output-control section to the typewriter- and real-time-clock section. From there it is transferred in parallel to the typewriter.

Figure 1-13. Data Flow During Typewriter Interrupt, and Sense-Flip-Flop Instructions, Functional Block Diagram

During the execution of the instructions which transfer one alphanumeric character from the typewriter to the Ar, the character is first transferred from the typewriter to the typewriter-buffer register. The four numeric bits are then transferred to the main adder and the two zone bits are transferred to bit-positions 5 and 6 of the CCr. The complete word in the CCr is transferred through the adder to the Ar specified by the AR/XO-field.

#### 1-57. Data Flow During Input-Output Operations